أخبار

يستكشف DAC دور AI و ML عبر الأسواق

سيستضيف مركز موسكون ، سان فرانسيسكو ، مؤتمر DAC من 25 إلى 28 يونيو

حلول OneSpin و Austemper نظم التصميم على حد سواء تسليط الضوء على أدوات للتحقق سلامة العمل. سيركز Austemper على تطوير نظام المهام الحرجة ، مع مجموعة أدوات KaleidoScope التي تدعم التصميم التماثلي للانتشار المتزامن المختلط للإشارات. يحتوي مجموعة الأدوات الآلية على إمكانات تحليل السلامة والتوليف والتحقق من التطبيقات الموجهة إلى الشهادات. يتم استخدامه لتصميمات السيارات على نطاق واسع في ADAS والقيادة الذاتية. تتضمن محاكاة الأعطال المتزامنة عمليات محاكاة موصى بها بواسطة المواصفة القياسية ISO 26262 للتوافق مع متطلبات ASIL.

وقد دخلت الشركة مؤخراً في شراكة مع OneSpin Solutions لتبني منهجية مدعومة بأداة لتطبيقات السلامة الوظيفية ، تجمع بين التصميم وتدفق التحقق ، والذي سيتم عرضه في جناح OneSpin. يتم إدخال آليات أمان الأجهزة في تصميمات الشرائح ، كما أن أدوات OneSpin Solutions تحقق رسميًا من منطق سلامة الأجهزة. يضمن التحقق من التكافؤ أن منطق الأمان المدرج لا يؤثر على الوظائف العادية والتحقق من اكتشاف الأخطاء يتحقق من أن آليات السلامة تعمل بشكل صحيح في حالة حدوث أخطاء عشوائية.

كما تقوم OneSpin بالترويج لمجموعة أدوات تأهيل الأدوات الخاصة بها ، بعد قيام TÜV S verificationD بالتحقق من عمليات تطوير الأداة الخاصة بها. تتوفر المجموعة الأولية لأداة الشركة 360 EC-FPGA EDA ، وهي عبارة عن فحص مكافئ تسلسلي تلقائي يمنع تدفقات تصميم FPGA من إدخال أخطاء التنفيذ. هذه المجموعة معتمدة للمواصفة ISO 26262 و IEC 61508 و EN 50128.

رؤى FPGA

لا يزال مع تصميم FPGA ، Plunify تعاونت مع Xilinx لتقديم مجموعة تصميم Vivado في السحابة ، عبر منصة Plunify Cloud. يدفع المصممون مبلغ 50c لتجميع مشروع Vivado على سحابة خدمات Amazon Web Services (AWS) ، بما في ذلك التراخيص.

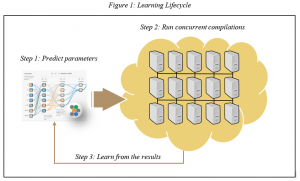

وستعرض الشركة أيضًا تحسينات على برنامج إغلاق توقيت InTime لتحسين توقيت FPGA في السحابة (الشكل 1). InTime Optimization منهجية يمكن أن تحسّن تردد الساعة بنسبة 20 إلى 80٪ وتفي بمتطلبات التوقيت في أيام ، بدلاً من أسابيع عبر التعلم الآلي. كما يعمل البرنامج على تسريع إغلاق التوقيت والتحسين ويتم الوصول إليه عبر السحابة.

وستعرض الشركة أيضًا تحسينات على برنامج إغلاق توقيت InTime لتحسين توقيت FPGA في السحابة (الشكل 1). InTime Optimization منهجية يمكن أن تحسّن تردد الساعة بنسبة 20 إلى 80٪ وتفي بمتطلبات التوقيت في أيام ، بدلاً من أسابيع عبر التعلم الآلي. كما يعمل البرنامج على تسريع إغلاق التوقيت والتحسين ويتم الوصول إليه عبر السحابة.

تعزيز تقنية eFPGA ، Achronix Semiconductor تتعاون مع متخصص IP المصبوب لزيادة الإنتاجية وتحقيق وفورات في تخزين الذاكرة.

سوف يشرح العارضان كيف تم نقل عنوان IP الخاص بضغط CAST دون ضياع إلى محفظة Achronix FPGA لاستخدامها في مركز البيانات وتطبيقات نقل البيانات المتنقلة. تطبيق الأجهزة لمعيار الضغط بدون ضياع لـ Deflate و GZIP و ZLIB ، متوافق مع تطبيقات البرامج المستخدمة للضغط أو إلغاء الضغط لتوفير ما يصل إلى 100 جيجابت / ثانية مع انخفاض الضغط وانخفاض زمن الوصول ، إلى جانب تقنية Speedcore eFPGA لنقل وتخزين كبير البيانات عند انخفاض استهلاك الطاقة.

قامت CAST بنقل IP الخاص بها إلى FPGA الخاصة بـ Achronix

كفاءة الطاقة

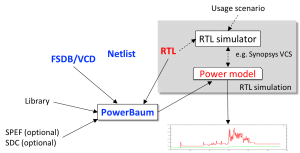

الحديث عن إدارة الطاقة ، عارض آخر ، باوم، ويحدد كفاءة الطاقة باعتبارها المنطقة الأكثر نموا في تصميم رقاقة. تم تصميم أداة تحليل الطاقة الآلية ونمذجتها من أجل مشاريع السيارات وإنترنت الأشياء والمحمول والشبكات والخوادم. يدعم الإصدار PowerBaum 2.0 (الشكل 3) الطاقة الديناميكية والثابتة ، مع الأخذ في RTL وأوصاف netlist ، ويضيف دعمًا لتحليل الطاقة مع مضاهاة الأجهزة. هذا ، كما تقول الشركة ، يسمح للمهندسين بإصلاح أخطاء الطاقة في سيناريوهات البرامج الواقعية. تدعم الأداة أيضًا التحليل مع درجات حرارة عشوائية يحددها المصممون ، لتقييم آثار درجة الحرارة على استهلاك الطاقة في التصميم.

في DAC ، ستقوم الشركة أيضا بإدخال PowerWurzel ، وهو محرك تحليل الطاقة على مستوى البوابة ليتم دمجه مع PowerBaum لنمذجة الطاقة.

الشكل 3 أدوات Baum لتحليل كفاءة الطاقة

أدوات تصميم وتسجيل SWC مبنية على السحابة لتصميم IC المقاييس تضمين Cloud Simulator و Verification Manager ، المصمم لإدارة متطلبات وموارد المحاكاة وتعديلها لأعلى أو لأسفل كل دقيقة. تدّعي الشركة أن Google Cloud تعمل على تمكين سعة محاكاة SystemVerilog متوافقة مع UVM غير محدودة وإدارة التحقق المحلية المستندة إلى الويب لأوقات الانحدار الأسرع وأخطاء رموز الشنطة الأقل وتغطية الكود القابلة للتنبؤ.

وبصرف النظر عن العارضين ، يستضيف الحدث جلسات تقنية وبرنامج من الأسئلة الرئيسية التي تتناول المجالات الموضعية. هذا العام ، على سبيل المثال ، سوف تستضيف Cadence برنامجًا تعليميًا حول "السلامة الوظيفية والموثوقية لتطبيقات السيارات" ، وواحدًا عن التعلم الآلي ("تعلم الآلة يأخذ أداء التعرف على الكلام إلى المستوى التالي"). وستركز إحدى الكلمات الرئيسية التي ألقتها آنا كاترينا شيدلتسكي ، فاشنال ، يوم الاثنين 25 يونيو ، على "أتمتة الذكاء: تعلم الآلة ومستقبل التصنيع". يستكشف استخدام ML و AI للروبوتات المساعدة اجتماعيًا (SAR) في حلقة رئيسية يوم الخميس من قبل Maja Matarić ، جامعة جنوب كاليفورنيا ، والتي ستقدم "Automation vs Augmentation: Social Assistive Robotocs and the Future of Work".

وهناك دعوة رئيسية أخرى تدعو شركة RISC-V كوسيلة لتحرير المعماريين من معماريات مجموعة التعليمات (ISAs). سيقدم كل من David A Patterson و Google وجامعة كاليفورنيا "عصرًا ذهبيًا جديدًا للهندسة الحاسوبية: المسرعات المحددة للنطاق و Open RISC-V".

منطقة جديدة هذا العام في DAC هي زقاق تصميم البنية التحتية. المبادرة من قبل تحالف ESD و جمعية لمهنيي الحوسبة عالية الأداء هي منطقة مخصصة للبنية التحتية لتكنولوجيا المعلومات لتصميم الأنظمة والمكونات الإلكترونية. بالإضافة إلى متطلبات الحوسبة والتخزين لتصميم وإدارة استخدام السحابة ، هناك مسرح مخصص مصمم على السحابة يناقش إدارة التراخيص والحوسبة الشبكية وأمن البيانات.