#### **Features and Benefits**

- Three independent low-side DMOS output drivers

- Short-circuit protection of drivers

- Eliminates need for flyback diodes on relays

- Thermal shutdown

- Separate precision 5 V regulator (2%)

- Current clamp on 5 V regulator

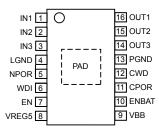

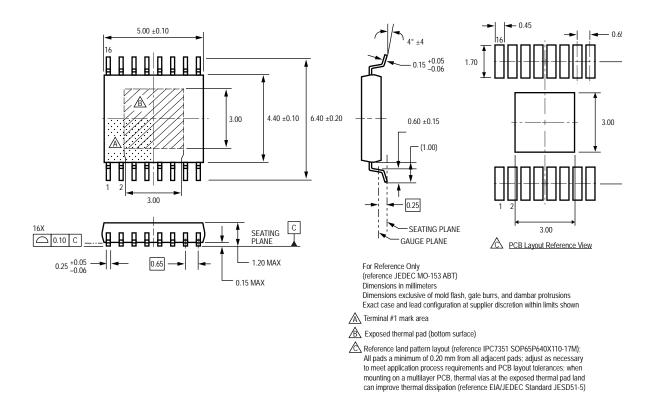

- 16-pin TSSOP package with exposed thermal pad

- Programmable reset (NPOR) delay time

- Programmable watchdog

- Automotive voltage and temperature ranges

- Active clamps for automotive load dump specifications

- Lead (Pb) free

## Package: 16 pin TSSOP (suffix LP) with exposed pad

Approximate Scale

## **Description**

Large numbers of relay-based applications require the use of a microprocessor which implements complex system control. In these systems, there is the need for microprocessor logic supply voltage, power-on reset circuitry, and watchdog capabilities. The Allegro™ A2550 combines the functions of voltage regulator, watchdog, and reset, as well as three low-side DMOS relay driver outputs. Primarily targeted at automotive applications, this IC is designed to provide robust performance over extended voltage and temperature ranges.

Three low-side DMOS drivers can drive inductive loads, such as relay coils. Each driver integrates rugged voltage clamps which survive automotive load dump pulses up to 48 V. The 40 V rating on VBB also ensures adequate survival in harsh automotive environments.

A 5 V linear regulator provides 40 mA of output current, with a tolerance of 2% over the operating temperature range. To enhance the usefulness of the IC in automotive applications, the 5 V regulator output, as well as the three low-side driver outputs are protected against overcurrent conditions.

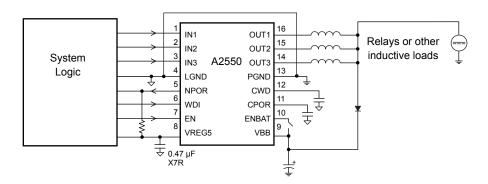

## **Typical Application**

Continued on the next page...

## A2550

# Relay Driver with 5 V Regulator for Automotive Applications

## **Description (continued)**

The A2550 also includes power-on reset circuitry (NPOR) as well as an integrated watchdog circuit. Combined, they service the monitoring and reset requirements of a system microprocessor.

The A2550 is supplied in a 16-pin TSSOP package with exposed thermal pad (package LP). The package is lead (Pb) free, with 100% matte tin leadframe plating.

#### **Selection Guide**

| Part Number  | Packing                       |

|--------------|-------------------------------|

| A2550KLPTR-T | 13-in. reel, 4000 pieces/reel |

## **Absolute Maximum Ratings**

| Characteristic                    | Symbol               | Notes                                                                                                              | Rating     | Units |

|-----------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|------------|-------|

| Supply Voltage                    | $V_{BB}$             |                                                                                                                    | -0.3 to 60 | V     |

| High Voltage Enable               | V <sub>ENBAT</sub>   |                                                                                                                    | -0.3 to 60 | V     |

| Output Driver                     | V <sub>OUT</sub>     | Continuous rating; outputs off                                                                                     | -1.4 to 48 | V     |

| Output Load Clamp                 | V <sub>OUT(CL)</sub> | Transient rating                                                                                                   | 60         | V     |

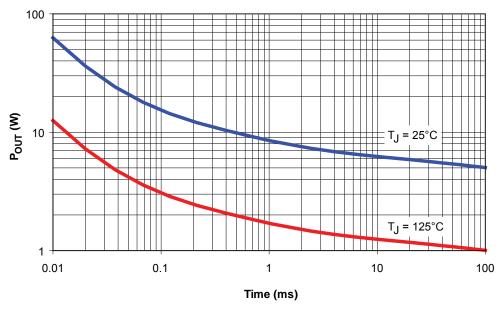

| Maximum Energy at Outputs         | E <sub>OUT</sub>     | Single Pulse, T <sub>J</sub> (initial) = 125°C                                                                     | 100        | mJ    |

| Peak Power Dissipation at Outputs | P <sub>PK</sub>      | Single pulse, $T_J$ (initial) = 125°C, $\Delta t$ = 1 ms; see figure 2 for different durations and $T_J$ (initial) | 1.7        | W     |

| All other pins                    |                      |                                                                                                                    | -0.3 to 7  | V     |

| ESD Rating – Human Body Model     |                      | AEC-Q100-002; all pins                                                                                             | 2.5        | kV    |

| ESD Rating – Charged Device Model |                      | AEC-Q100-011; all pins                                                                                             | 1050       | V     |

| Operating Ambient Temperature     | T <sub>A</sub>       | Range K                                                                                                            | -40 to 125 | °C    |

| Maximum Junction Temperature      | T <sub>J (max)</sub> |                                                                                                                    | 150        | °C    |

| Storage Temperature               | T <sub>stg</sub>     |                                                                                                                    | -55 to 150 | °C    |

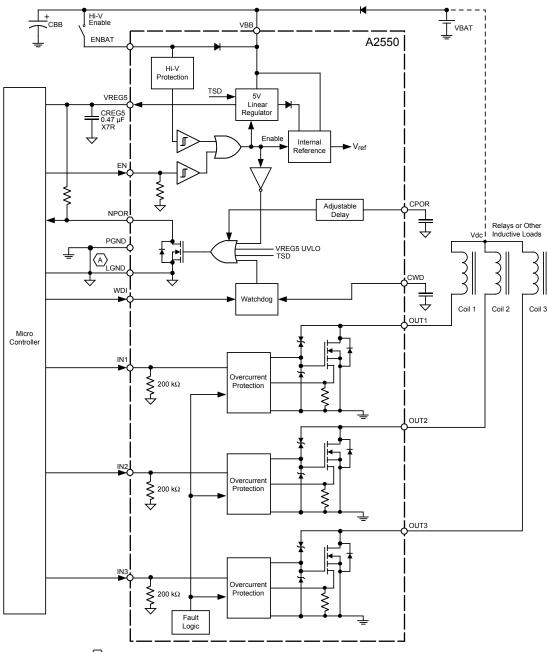

## **Functional Block Diagram**

A LGND and PGND must be connected externally.

Component Selection Table

| Component Con | ootioii iabio              |                                   |

|---------------|----------------------------|-----------------------------------|

| Name          | Suitable Characteristics   | Representative Device             |

| CBB           | 33 µF, 63 V electrolytic   | United Chemi-Con EGXE630E330MH12D |

| CREG5         | 0.47 µF, 25 V, X7R ceramic |                                   |

| CWD. CPOR     | 0.22 uF. 16 V. X7R ceramic |                                   |

3

ELECTRICAL CHARACTERISTICS, -40°C ≤ T<sub>J</sub> ≤ 150°C, V<sub>BB</sub> within operating limits, unless otherwise noted

| Characteristics                                 | Symbol               | Test Conditions                                                                                        | Min.       | Тур. | Max.     | Units |

|-------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------|------------|------|----------|-------|

| Supply                                          | *                    |                                                                                                        |            |      |          |       |

| VBB Operating Voltage <sup>1</sup>              | $V_{BB}$             |                                                                                                        | 7          | _    | 40       | V     |

|                                                 | I <sub>BBQ</sub>     | All OUTx Off; EN = 5 V, V <sub>BB</sub> = ENBAT = 14 V                                                 | -          | _    | 4        | mA    |

| VBB Supply Current                              | I <sub>BB</sub>      | All OUTx On; EN = 5 V, V <sub>BB</sub> = ENBAT= 14 V                                                   | T -        | -    | 5        | mA    |

|                                                 | I <sub>BBS</sub>     | Sleep mode, EN = ENBAT = 0                                                                             | T -        | -    | 10       | μΑ    |

| Logic Inputs                                    | •                    |                                                                                                        |            |      |          |       |

| ENBAT Input Voltage <sup>2</sup>                | V                    | HIGH input level                                                                                       | 3.5        | _    | $V_{BB}$ | V     |

| ENDAT Input Voltage <sup>2</sup>                | V <sub>ENBAT</sub>   | LOW input level                                                                                        | 0          | _    | 1.5      | V     |

| EN, WDI, and INx Input Voltage                  | V <sub>IH</sub>      | HIGH input level                                                                                       | 3.5        | _    | 5.5      | V     |

| EN, WDI, and INX input voitage                  | V <sub>IL</sub>      | LOW input level                                                                                        | 0          | _    | 1.5      | V     |

| ENBAT, EN, WDI, INx Input Voltage<br>Hysteresis | V <sub>Ihys</sub>    |                                                                                                        | 200        | _    | _        | mV    |

|                                                 |                      | HIGH input level, $V_{BB} = V_{BB(max)}$                                                               | <b>-</b>   | _    | 400      | μΑ    |

| ENBAT Input Current <sup>2,3</sup>              | I <sub>ENBAT</sub>   | HIGH input level, V <sub>BB</sub> = 14 V                                                               | <b> </b> - | _    | 70       | μΑ    |

|                                                 |                      | LOW input level                                                                                        | -50        | _    | 10       | μΑ    |

| EN Input Current?                               | ,                    | HIGH input level                                                                                       | -          | _    | 50       | μΑ    |

| EN Input Current <sup>2</sup>                   | I <sub>EN</sub>      | LOW input level                                                                                        | -50        | _    | 10       | μΑ    |

| MDI Innut Current?                              |                      | HIGH input level                                                                                       | _          | _    | 50       | μΑ    |

| WDI Input Current <sup>2</sup>                  | I <sub>WDI</sub>     | LOW input level                                                                                        | -10        | _    | 10       | μA    |

| INIv Innova Comment?                            |                      | HIGH input level                                                                                       | -          | _    | 50       | μA    |

| INx Input Current <sup>2</sup>                  | I <sub>INx</sub>     | LOW input level                                                                                        | -10        | _    | 10       | μA    |

| Drivers                                         |                      | ,                                                                                                      | 1          | 1    | 1        |       |

| Description Deleve                              | t <sub>p(ON)</sub>   | INx change to unloaded output change                                                                   | T -        | 1    | 2        | μs    |

| Propagation Delays                              | t <sub>p(OFF)</sub>  | INx change to unloaded output change                                                                   | <b>-</b>   | 0.5  | 1        | μs    |

|                                                 | R <sub>DS(on)</sub>  | I <sub>OUTx</sub> = 250 mA, V <sub>BB</sub> = 14 V                                                     | <b>-</b>   | -    | 5        | Ω     |

| Driver On-Resistance                            |                      | I <sub>OUTx</sub> = 250 mA, V <sub>BB</sub> = 9 V                                                      | <b>-</b>   | -    | 5.5      | Ω     |

|                                                 |                      | I <sub>OUTx</sub> = 250 mA, V <sub>BB</sub> = 7 V                                                      | <b>-</b>   | -    | 6        | Ω     |

| Driver Leakage Current                          | I <sub>DSS</sub>     | V <sub>OUTx</sub> = 40 V                                                                               | <b>-</b>   | -    | 10       | μΑ    |

| Diode Forward Voltage                           | V <sub>F</sub>       | I <sub>OUTx</sub> = -250 mA                                                                            | <b>-</b>   | -1.3 | -1.4     | V     |

| Output Clamp Voltage                            | V <sub>CL</sub>      | I <sub>OUTx</sub> = 100 μA                                                                             | 50         | -    | 60       | V     |

| Low-Side Driver Overcurrent (O.C.) Threshold    | I <sub>OUT(OC)</sub> | OOIA                                                                                                   | 275        | -    | 500      | mA    |

| Blanking Time Before Overcurrent Detect         | t <sub>BLANK</sub>   | I <sub>OUT</sub> = 500 mA                                                                              | 2          | _    | 20       | μs    |

| Regulator                                       | DE WITE              | 1 001                                                                                                  |            | 1    | 1        |       |

| Voltage Regulator Output Voltage                | V <sub>REG5</sub>    | $C_{REG5} \ge 0.47 \ \mu F \ (X7R \ Ceramic, \ ESR \le 0.5\Omega),$<br>1 mA $\le I_{REG5} \le 40 \ mA$ | 4.9        | 5.0  | 5.1      | V     |

| Pass Transistor On-Resistance <sup>1</sup>      | R <sub>REG5</sub>    | I <sub>REG5</sub> = 40 mA                                                                              | <b>-</b>   | -    | 55       | Ω     |

| Line Regulation Voltage                         | V <sub>LNR</sub>     | I <sub>REG5</sub> = 1 mA                                                                               | <u> </u>   | _    | 20       | mV    |

| 1 15 15 17                                      |                      | 1 mA $\leq$ I <sub>REG5</sub> $\leq$ 40 mA, V <sub>BB</sub> = 7 V                                      | <u> </u>   | _    | 100      | mV    |

| Load Regulation Voltage                         | $V_{LDR}$            | 1 mA ≤ I <sub>REG5</sub> ≤ 40 mA, V <sub>BB</sub> ≥ 9 V                                                | <u> </u>   | _    | 40       | mV    |

|                                                 |                      | V <sub>REG5</sub> = 4.63 V, V <sub>BB</sub> = 7 V                                                      | 40         | _    | 150      | mA    |

| Current Limit Level <sup>4</sup>                | I <sub>REG5Lim</sub> | V <sub>REG5</sub> = 4.63 V, V <sub>BB</sub> ≥ 9 V                                                      | 65         | _    | 200      | mA    |

|                                                 | IXEGULIII            | V <sub>REG5</sub> = 0 V                                                                                | 65         | _    | 200      | mA    |

|                                                 | 1,,                  | V <sub>REG5</sub> falling                                                                              | 4.25       | 4.38 | 4.63     | V     |

| Linder Voltage Lockout Threshold                | V <sub>UVREG5</sub>  | V states                                                                                               |            |      | 4.75     | V     |

| Under Voltage Lockout Threshold                 | UVILLUS              | V <sub>REG5</sub> rising                                                                               | 4.36       | 4.50 | 4.70     | , v   |

Continued on the next page...

ELECTRICAL CHARACTERISTICS, continued -40°C ≤ T<sub>J</sub> ≤ 150°C, V<sub>BB</sub> within operating limits, unless otherwise noted

| Characteristics                        | Symbol                 | Test Conditions                                                                                | Min. | Тур. | Max. | Units |  |

|----------------------------------------|------------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Watchdog and Power-On Reset            | •                      |                                                                                                |      |      |      |       |  |

| NPOR Active Voltage                    | V <sub>NPOR</sub>      | $I_{NPOR} = 1 \text{ mA}; V_{REG5} = 1.5 \text{ V}; 1.5 \text{ V} \le V_{BB} \le 40 \text{ V}$ | _    | _    | 400  | mV    |  |

| NPOR Inactive Leakage Current          | I <sub>NPOR(Off)</sub> | V <sub>NPOR</sub> = 5 V                                                                        | _    | _    | 10   | μA    |  |

| CWD and CPOR Trip Voltage              | V <sub>TRIP(H)</sub>   | $V_{TRIP(H)} = V_{REF}$                                                                        | _    | 1.2  | _    | V     |  |

| CVVD and or one mp voltage             | V <sub>TRIP(L)</sub>   |                                                                                                | _    | 0.2  | _    | V     |  |

| CPOR Charge Current                    | I <sub>POR</sub>       |                                                                                                | 2.5  | 5    | 7.5  | μA    |  |

| Power-On Reset Cycle Time <sup>5</sup> | t <sub>POR</sub>       | $C_{POR} = 0.22  \mu F$                                                                        | _    | 44   | _    | ms    |  |

| CWD Charge Current                     | 1                      | Charging                                                                                       | 2.5  | 5    | 7.5  | μA    |  |

| CVVD Charge Current                    | ICWD                   | Discharging                                                                                    | _    | 70   | _    | μA    |  |

| Thermal Protection                     |                        |                                                                                                |      |      |      |       |  |

| Thermal Shut Down Threshold            | T <sub>TSD</sub>       |                                                                                                | 150  | 175  | _    | °C    |  |

| Thermal Shut Down Hysteresis           | T <sub>TSDhys</sub>    |                                                                                                | -    | 15   | _    | °C    |  |

$<sup>^1</sup>$ See Applications Information section for operation with  $V_{BB}$  < 7 V. For  $V_{BB}$  > 24 V, thermal constraints limit regulator current.

#### THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

| Characteristic                      | Symbol            | Test Conditions*                                                                                            |      | Units |

|-------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|------|-------|

| Thermal Resistance, Junction to Pad | $R_{\theta JP}$   |                                                                                                             | 2    | °C/W  |

| Thermal Resistance, Junction to     | R <sub>e.IA</sub> | 4-layer PCB based on JEDEC standard                                                                         | 34   | °C/W  |

| Ambient                             |                   | 2-layer PCB with 2 in.2 copper both sides                                                                   | 44   | °C/W  |

| Maximum Allowable Power Dissipation | P <sub>D</sub>    | $R_{\theta JA}$ = 44 °C/W (estimated), 2-layer PCB with 2.0 in. <sup>2</sup> of 2 oz. copper, $T_A$ = 125°C | 0.57 | W     |

| maximum Allowable Fower Dissipation |                   | $R_{\theta JA}$ = 44 °C/W (estimated), 2-layer PCB with 2.0 in. <sup>2</sup> of 2 oz. copper, $T_A$ = 85°C  | 1.48 | W     |

<sup>\*</sup>Additional thermal data available on the Allegro Web site.

<sup>&</sup>lt;sup>2</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

$<sup>^{3}</sup>$ When  $V_{ENBAT}$  exceeds  $V_{BB}$  it is clamped with a diode. ( $V_{ENBAT} - V_{BB}$ ) ≤ 1.2 V at 40 mA.

<sup>&</sup>lt;sup>4</sup>Defined as the maximum current level allowed during excessive load condition.

<sup>&</sup>lt;sup>5</sup>See Applications Information section for calculations. Values guaranteed by design, and depend on capacitor tolerances.

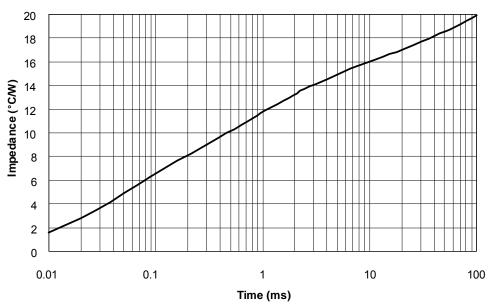

### **Dynamic Thermal Impedance**

Square Wave Power Pulse in a Single Output Stage

Figure 1. Dynamic thermal impedance of an individual output stage during active clamp of an inductive load (mounted on a 4-layer PCB based on JEDEC standard).

## **Nonrepetitive Output Active Clamp Power Dissipation**

Figure 2. Peak power dissipation curves for nonrepetitive clamped outputs. Output voltage is clamped during turn-off of inductive loads while current decays.

## **Functional Description**

### **Pin Descriptions**

**EN** Enable pin; logical OR with ENBAT. This logic-level input enables the A2550. If there are no faults, the regulator is live and outputs can be switched. When both the EN and ENBAT pins are held low, the A2550 enters Sleep mode.

**ENBAT** Enable pin; logical OR with EN. Same as EN, except that this pin is high-voltage protected, and specified up to  $V_{BB}$  so it can be tied to the battery or power source. Not to exceed  $V_{BB}$  because the ESD structure places a diode between the ENBAT and VBB pins.

**WDI** Watchdog Input. Monitors the microcontroller to detect when it stops functioning. This pin is connected to an edge trigger. To avoid a fault, the latter must be triggered before CWD times-out. When not used, WDI is defeated by tying it to NPOR and shorting CWD.

**CWD** Watchdog timer capacitor terminal. Used with WDI. A current source charges the external capacitor tied to this pin. A reverse current source discharges the capacitor when either WDI transitions or the high Trip Voltage, V<sub>TRIP(H)</sub>, is reached (see specification table for values). The charge-up time defines the maximum period allowed WDI to toggle before a fault is issued; the charge-down time defines the width of NPOR pulses issued to wake-up the microcontroller

**NPOR** NOT Power On Reset. This active-low pin indicates a fault. Except for watchdog faults, NPOR is held low during the fault state. Refer to the Fault Logic table to determine

which faults are latched. Watchdog faults generate a train of pulses to "wake up" the microcontroller.

**CPOR** Power-On Reset timer capacitor terminal. Whenever VREG5 first charges up (at start-up or when a fault is cleared) a "fault" condition remains in effect until the onboard current source drives CPOR to the high Trip Voltage,  $V_{TRIP(H)}$ . This allows external circuits, such as a microcontroller, to be initialized before activating the outputs. CPOR is defeated by pulling it high to VREG5 with a 50 k $\Omega$  resistor.

**INx** Input pin. Active-high CMOS input. Internally tied to 200 k $\Omega$  pull-down resistors.

**OUTx** Output pin. Open drain DMOS. Clamps to a voltage greater than  $V_{BB}$  when an inductive load is switched off. Includes current mirror for overcurrent protection.

**VBB** Power pin, or "battery." Specified for automotive voltages.

**VREG5** 5 V Regulator output. Clamped at the Current Limit Level (I<sub>REG5Lim</sub>) for excessive loads. As load resistance decreases, VREG5 is pulled below the UVLO level. In that case, a fault is generated (NPOR low).

**LGND** Logic Ground. The reference pin for the logic circuits. Must be connected to PGND externally.

**PGND** Power Ground. The reference pin for the outputs (OUTx). Must be connected to LGND externally.

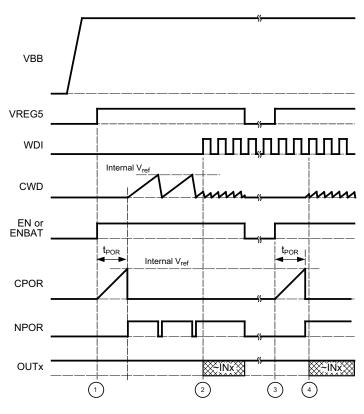

## Timing Diagram: Initial Start-up and Exiting Sleep Mode

- 1. 5 V signal to wake up microcontroller.

- 2. OUTx enabled with first watchdog pulse.

- 3. Power ramp-up sequence with watchdog active.

- 4. NPOR inactive, but outputs not enabled until watchdog detected.

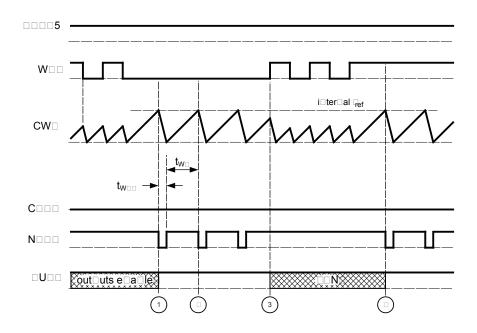

## Timing Diagram: Watchdog Monitoring

- 1. Missing watchdog detected (WDI low).

- 2. NPOR pulses generated periodically.

- 3. NPOR inactive, but outputs not enabled until watchdog detected.

- 4. Missing watchdog detected (WDI low, steps 2 and 3 repeat).

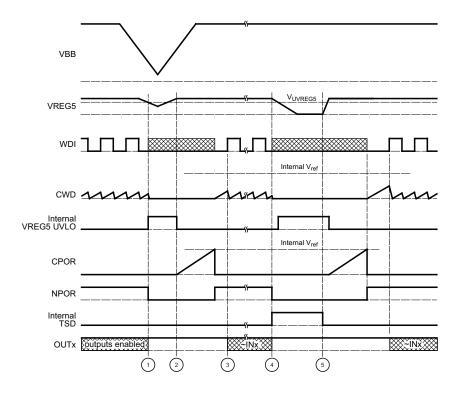

## Timing Diagram: VREG5 UVLO and TSD Monitoring

- 1. VREG5 undervoltage detected.

- 2. VREG5 recovers, and after it rises above  $V_{UVREG5} + V_{UVREG5(Hys)}$ , UVLO flag is deactivated and CPOR recharges.

- 3. NPOR inactive, but outputs not enabled until watchdog detected.

- 4. TSD event detected and NPOR is activated. When  $V_{REG5} \le V_{UVREG5}$ , VREG5 shuts down.

- 5. TSD flag deactivated (VREG5 allowed to rise; steps 2 and 3 repeat)

## **Applications Information**

## **Dropout Voltage**

For operation with  $V_{BB}$  below the specified range of operating voltages, use the Pass Transistor On-Resistance  $R_{REG5}$  to determine the maximum allowed regulator current,  $I_{REG5(max)}$ . This current is limited by the difference between  $V_{BB}$  and  $V_{REG5}$ , according to the following equation:

$$I_{\text{REG5}} < \frac{V_{\text{BB}} - V_{\text{REG5}}}{R_{\text{REG5}}} \tag{1}$$

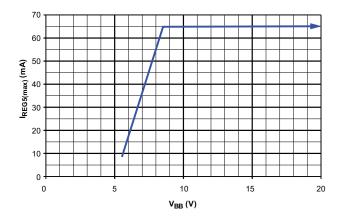

Figure 3 shows the results of this condition combined with the rated regulator current, in normal operation.

Note that, although the regulator is specified for normal operation with  $V_{BB}$  well above normal automotive voltages, in general thermal constraints will limit maximum operational  $V_{BB}. \label{eq:basic_problem}$

## **Fault Logic**

The A2550 offers several protection and fault detection features. The operation of thermal shutdown, watchdog monitoring of the microcontroller, and regulated voltage undervoltage lockout are described in the Timing Diagrams section. The fault logic is described in table 1.

#### **NPOR**

The following faults generate a RESET state:

- · watchdog alarm

- VREG5 falls below the UVLO level In addition, the following conditions cause a low NPOR signal *if* the NPOR pin is pulled up by VREG5 (because these conditions disable VREG5):

- overtemperature (Thermal Shut Down)

- no ENABLE signal (EN = ENBAT = 0)

Figure 3. Current Capability of the 5 V Regulator (VREG5)

Table 1. Fault Logic<sup>a</sup>

| Inputs                      |     |      |                   |     |             | Out   | puts  |      |                                                                           |  |

|-----------------------------|-----|------|-------------------|-----|-------------|-------|-------|------|---------------------------------------------------------------------------|--|

| EN OR<br>ENBAT <sup>b</sup> | TSD | UVLO | Watchdog<br>alarm | OCx | Internal 5V | VREG5 | NPOR  | OUTx | Mode of Operation                                                         |  |

| 1                           | 0   | 0    | 0                 | 0   | 1           | 1     | 1     | INx  | Normal Operation: OUTx active for INx active.                             |  |

| 1                           | 0   | 0    | 0                 | 1   | 1           | 1     | 1     | Z    | OCx disables OUTx only. OUTx latched OFF until INx removed and reapplied. |  |

| 1                           | 0   | 0    | 1                 | Х   | 1           | 1     | Pulse | Z    | NPOR periodically pulses to attempt RESET of microcontroller.             |  |

| 1                           | 0   | 1    | Х                 | Х   | 1           | 1     | 0     | Z    | NPOR remains active after UVLO recovers until POR delay expires.          |  |

| 1                           | 1   | Х    | Х                 | Х   | 1           | 0     | 0     | Z    |                                                                           |  |

| 0                           | Х   | Х    | Х                 | Х   | 0           | 0     | Off   | Z    | Sleep mode. NPOR = 0 when pulled up by VREG5 because VREG5 = 0.           |  |

<sup>&</sup>lt;sup>a</sup>X indicates "don't care," Z indicates high impedence.

bThis entry is a logical OR of the EN and ENBAT pins.

## **Applications Information**

NPOR is pulsed for a watchdog fault. For the remaining faults, NPOR is held low for the duration of the fault. After the fault condition is removed, NPOR remains low during the t<sub>POR</sub> period. The latter is set by the value of the external capacitor fed by a current source at the CPOR pin, according to the following formula:

$$t_{\text{POR}} = \left(200 \frac{\text{ms}}{\mu \text{F}}\right) \times C_{\text{POR}}$$

(2)

The scaling factor is simply derived from the specifications using the typical value of I<sub>POR</sub>:

$$\frac{t_{\text{POR}}}{C_{\text{POR}}} = \frac{V_{\text{REF}} - V_{\text{TRIP(L)}}}{I_{\text{POR}}}$$

(3)

#### Watchdog

The watchdog monitors the microcontroller to detect if it locks up. To do so, the watchdog checks for pulses on the Watchdog Input pin (WDI), and if they are absent for longer than the timeout period, t<sub>WD</sub>, the watchdog activates NPOR, which pulses periodically. t<sub>WD</sub> is proportional to the external capacitor fed by a current source at the CWD pin. The voltage change is 1 V, so using the typical value of I<sub>CWD</sub>(charging) we have:

$$t_{\rm WD} = \left(200 \, \frac{\rm ms}{\mu \rm F}\right) \times C_{\rm WD} \tag{4}$$

The pulse width for NPOR active, twopR, also scales proportionally to the value of the external capacitor at the CWD pin. Using the typical value of I<sub>CWD</sub>(discharging) we have:

$$t_{\text{WDR}} = \left(14 \frac{\text{ms}}{\mu \text{F}}\right) \times C_{\text{WD}} \tag{5}$$

See the specification tables for tolerances.

When not used, disable watchdog by tying WDI to NPOR and tying CWD low. Table 2 shows watchdog timing for the nominal capacitances listed.

Table 2. Timing Set by Capacitors

| C<br>(µF) | t <sub>POR</sub><br>(ms) | t <sub>WD</sub><br>(ms) | t <sub>WDR</sub><br>(ms) |

|-----------|--------------------------|-------------------------|--------------------------|

| 0.1       | 20                       | 20                      | 1                        |

| 0.22      | 44                       | 44                      | 3                        |

| 0.47      | 94                       | 94                      | 7                        |

| 1         | 200                      | 200                     | 14                       |

### **Output Overcurrent**

When the OC (overcurrent) protection is triggered in a driver, that driver is disabled for self-protection. No other functions are affected; NPOR and VREG5 operate normally. A disabled output driver remains shut down until the respective INx is brought low, then high again; at which time OUTx turns on. OUTx will switch on again the next time INx is applied. If a short-to-battery still exists, the overcurrent will trip each time INx is reapplied.

### Sleep

The A2550 is put to sleep by holding both EN and ENBAT low. In sleep mode all functions are shut down, including VREG5. If the VREG5 regulator is required at all times, disable sleep mode by tying ENBAT to VBB.

### **Power Limits**

Power dissipation, PD, is limited by thermal constraints. The maximum allowed power dissipation,  $P_{D(max)}$ , is found from the formula:

$$T_{\rm J} = (P_{\rm D(max)} \times R_{\rm \theta JA} + T_{\rm A}) \le T_{\rm J(max)}$$

(6)

The maximum junction temperature,  $T_{J(max)}$ , and the thermal resistance,  $R_{\theta JA}$ , are given in the specification tables.

The three main contributors to power dissipation are:

- P<sub>BIAS</sub> from the supply bias current

- P<sub>REG</sub> from the linear regulator voltage drop

- P<sub>LS</sub> from low-side driver conduction

For example, to determine if T<sub>J</sub> is in an acceptable range, given:

$$R_{\theta JA} = 55^{\circ}\text{C/W}$$

, and  $T_A = 125^{\circ}\text{C}$ ; and  $P_{BIAS} = V_{BB} \times I_{BBQ}$  (7)

$$= 14 \text{ V} \times 3 \text{ mA} = 42 \text{ mW}, \text{ and}$$

$$P_{\text{REG}} = (V_{\text{BB}} - V_{\text{REG5(min)}}) \times I_{\text{REG5}}$$

(8)

= (14 V - 4.9 V) × 20 mA= 182 mW, and

Allegro MicroSystems, LLC

1.508.853.5000; www.allegromicro.com

115 Northeast Cutoff

$$P_{LS} = (R_{DS(on)} \times I_{LS1}^2) + (R_{DS(on)} \times I_{LS2}^2) + (R_{DS(on)} \times I_{LS3}^2)$$

.

Because  $I_{\rm LS1} = I_{\rm LS2} = I_{\rm LS3} = 110 \ \rm mA$  , and given that  $R_{\rm DS(on)} = 5 \ \Omega$ , then

$$P_{LS} = 3(5 \Omega)*(110 \text{ mA})^2 = 182 \text{ mW}$$

.

Given also:

$$P_{D} = P_{BIAS} + P_{REG} + P_{LS}$$

= 42 mW + 182 mW + 182 mW = 406 mW.

$T_{\rm I}$  can be calculated by substitution into equation 6:

$$T_1 = 0.406 \text{ W} \times 55^{\circ}\text{C/W} + 125^{\circ}\text{C} = 147^{\circ}\text{C}$$

.

## **Reverse Battery**

The low-side driver outputs can withstand reverse battery when the load ( $R_{LOADx}$ ) is connected to limit current. Power dissipation ( $P_D = P_{LS(rvrs)}$ ) is limited by thermal constraints, according to the following formula:

$$P_{LS(rvrs)} = V_{F1} \times I_{F1} + V_{F2} \times I_{F2} + V_{F3} \times I_{F3} , \qquad (11)$$

where:

$$I_{Fx} = \frac{V_{\text{BB(rvrs)}} - V_{Fx}}{R_{\text{LOAD}x}} . \tag{12}$$

#### **Active Clamp on Outputs**

The driver section includes an active clamp that prevents an overvoltage when an inductive load is switched off. Zener diodes are connected at the output pins. This removes the need for external freewheeling diodes across inductive loads.

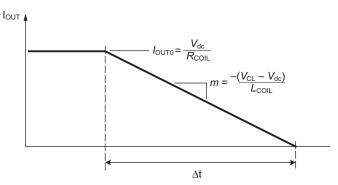

The coil current,  $I_{COIL}$ , is quenched by allowing the output pin voltage,  $V_{OUTx}$ , to exceed the battery voltage at the load,  $V_{dc}$ . This applies a negative voltage drop across the load. Therefore the current gradient is driven negative, as shown in the following formula:

$$\frac{dI_{\text{COIL}}}{dt} = \frac{V_{\text{dc}} - V_{\text{OUT}} - I_{\text{COIL}} \times R_{\text{COIL}}}{L_{\text{COII}}} < 0 . \tag{13}$$

The output voltage is clamped to protect the driver. The active clamp works as follows. The voltage at the driver output is pushed high by the inductive current. Once the clamp voltage,  $V_{CL}$ , is reached, a Zener diode conducts current to the internal FET gate driver block. Therefore, the FET turns partially on, in order to limit any further increase in voltage at the output pin. The output is then held at this clamp voltage until the current decays to zero, as shown in figure 4.

Energy loss in the chip, E, may be calculated as follows. Load coil resistance,  $R_{COIL}$ , is usually a significant value, but a worst case scenario takes  $R_{COIL} = 0$  for simplicity. With active clamping at  $V_{CL}$ , the output current (with initial value  $I_{OUT0}$ ) is driven low and the upper limit on energy loss in the driver is calculated as:

$$E_{\text{max}} = \frac{1}{2} I_{\text{OUT0}} V_{\text{CL}} \Delta t. \tag{14}$$

From figure 4:

$$\Delta t = \frac{L_{\text{COIL}} I_{\text{OUT0}}}{V_{\text{CI}} - V_{\text{do}}},\tag{15}$$

and

(9)

$$E_{\text{max}} = \frac{1}{2} L_{\text{COIL}} I_{\text{OUT0}}^2 (1 - V_{\text{dc}} / V_{\text{CL}})^{-1} . \tag{16}$$

Figure 4. Output Voltage Clamping

A more rigorous derivation, including R<sub>COIL</sub> during the exponential current decay results in:

$$i(t) = \frac{V_{\text{dc}}}{R_{\text{COIL}}} - \frac{V_{\text{CL}}}{R_{\text{COIL}}} \left[ 1 - \exp\left(-t \frac{R_{\text{COIL}}}{L_{\text{COIL}}}\right) \right] , \quad (17)$$

and

$$\Delta t = \frac{L_{\text{COIL}}}{R_{\text{COIL}}} \ln \left( 1 - V_{\text{dc}} / V_{\text{CL}} \right)^{-1}. \tag{18}$$

Energy loss in the driver is:

$$E = \frac{V_{\rm CL} \ V_{\rm DC} \ L_{\rm COIL}}{R_{\rm COIL}^2} [1 + (V_{\rm CL} / V_{\rm dc} - 1) \ln (1 - V_{\rm dc} / V_{\rm CL})] \ . \tag{19}$$

#### **Capacitive Loads**

When capacitive loads are applied to the outputs, the constraint described below applies. Such is the case, for example, when capacitors are attached to the outputs to protect against ESD. Larger capacitors protect against larger ESD voltages. However, the upper limit on capacitance is determined by the blanking time. The latter allows for spurious current spikes and capacitor discharges to be completed before the overcurrent detection circuit senses the output current (see  $t_{\rm BLANK}$  in the Electrical Characteristics table). The blanking time allows a 47 nF capacitor with 20% tolerance and nominal 12 V automotive voltages.

### **Pin-out Diagram**

### **Terminal List Table**

| rermin | ai List Table |                                                    |

|--------|---------------|----------------------------------------------------|

| No.    | Name          | Description                                        |

| 1      | IN1           | Activate driver 1                                  |

| 2      | IN2           | Activate driver 2                                  |

| 3      | IN3           | Activate driver 3                                  |

| 4      | LGND          | Logic ground; must be connected to PGND externally |

| 5      | NPOR          | Not Power-On Reset                                 |

| 6      | WDI           | WatchDog Input                                     |

| 7      | EN            | Enable (low voltage)                               |

| 8      | VREG5         | 5V regulator                                       |

| 9      | VBB           | Supply voltage                                     |

| 10     | ENBAT         | Enable (high voltage)                              |

| 11     | CPOR          | Capacitor terminal for Power-On Reset cycle time   |

| 12     | CWD           | Capacitor terminal for WatchDog timing             |

| 13     | PGND          | Power ground; must be connected to LGND externally |

| 14     | OUT3          | Low side driver 3                                  |

| 15     | OUT2          | Low side driver 2                                  |

| 16     | OUT1          | Low side driver 1                                  |

| _      | PAD           | Exposed pad for enhanced thermal performance       |

#### 16-Pin TSSOP (Suffix LP) with Exposed Pad

Copyright ©2006-2013, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com