# NS9210/NS9215 Errata

Part number/version: 90002007\_C Release date: November 2010

www.digi.com

# For use in conjunction with:

NS9210 Hardware Reference

Part number/version: 90000846\_H Release date: November 2010

NS9215 Hardware Reference

Part number/version: 90000847\_J Release date: November 2010 ©2010 Digi International Inc.

Printed in the United States of America. All rights reserved.

Digi, Digi International, the Digi logo, a Digi International Company, are trademarks or registered trademarks of Digi International, Inc. in the United States and other countries worldwide. All other trademarks are the property of their respective owners.

Information in this document is subject to change without notice and does not represent a commitment on the part of Digi International.

Digi provides this document "as is," without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of, fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are made periodically to the information herein; these changes may be incorporated in new editions of the publication.

Digi International 11001 Bren Road East Minnetonka, MN 55343 U.S.A. United States: +1 877 912-3444 Other locations: +1 952 912-3444 Fax: +1 952 912-4960 www.digi.com/support/

Online support: www.digi.com/support/eservice

www.digi.com

### SPI: Extra clock inserted in modes 1, 2, and 3

The Digi NS9210/NS9215 supports four SPI clocking modes. Each mode's characteristics are defined by the idle value of the clock, which clock edge captures data, and which clock edge drives data. The MODE field in the SPI Configuration register specifies the timing mode.

#### Issue:

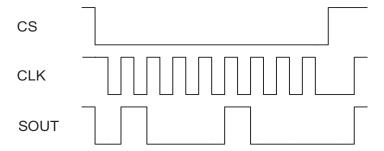

In SPI modes 1, 2, and 3 an unexpected additional clock is inserted after the last byte is transmitted. See timing diagrams below. A portion of the unexpected clock cycle occurs while CS is asserted. Unless the SPI device connected to the NS9210/NS9215 port is capable of handling this unexpected behavior, this may cause SPI communication issues.

#### SPI Mode 1

#### Workarounds:

- Select SPI Mode 0 instead and enable the inversion function using the INV bit (D01) in the corresponding GPIO Configuration Register of SPI CLK. This workaround will also be integrated as an option in a future version of the NET+OS SPI driver API.

- FIM-based SPI port with support for SPI Mode 1.

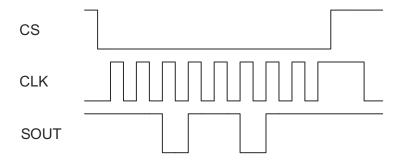

## SPI Mode 2

#### Workaround:

■ FIM-based SPI port with support for SPI Mode 2.

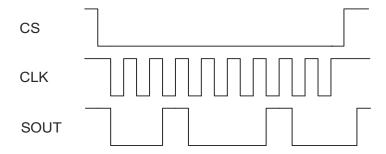

#### SPI Mode 3

#### Workaround:

■ FIM-based SPI port with support for SPI Mode 3.

For FIM-based SPI port implementation details please refer to the Digi NS9210/NS9215 FIM SPI Port Implementation Supplemental Reference, Digi part number 90002114\_A.

# **Change Log**

The following changes were made to this document in the revisions listed below.

#### **Revision A**

■ Initial Release.

#### **Revision B**

- Table 1: SPI Enable (CS) changed to GPIO[3], SPI In changed to GPIO[0].

- Table 2: SPI Enable (CS) changed to GPIO[29], SPI In changed to GPIO[26].

#### **Revision C**

■ Replaced extended FIM-based SPI Port content with a link to the Digi NS9210/9215 FIM SPI Port Implementation Supplemental Reference (Digi part number 90002114\_A).