### IXZ318N50 MOSFET and IXRFD631 Gate Driver Module

500 V 18 A 0.3 Ω

#### **Features**

- · Isolated substrate

- High isolation voltage (>2500 V)

- Excellent thermal transfer

- Increased temperature and power cycling capability

- IXYS advanced Z-MOS process for low parasitic capacitance

- Low R<sub>DS(ON)</sub>

- · Very low insertion inductance

- No Beryllium Oxide (BeO) or other hazardous materials

- Latch-up protected

- · Low quiescent supply current

- · RoHS compliant

### **Advantages**

- · Optimized for RF and high speed

- · Easy to mount, no insulators needed

- High power density

- Single package reduces size and heat sink area

## **Applications**

- Class D or E switching generators

- Switch mode power supplies (SMPS)

- Pulse generators

- Transducer driver

## **Description**

The IXZ631DF18N50 is a CMOS high-speed, high-current gate driver and MOSFET combination module specifically designed for Class D, E, HF, and RF applications at up to 27 MHz, as well as other applications. The IXZ631DF18N50 in pulse mode can provide 95 A of peak current while producing voltage rise and fall times of less than 5 ns, and minimum pulse widths of 8 ns. The input of the driver is fully immune to latch-up over the entire operating range. Designed with small internal delays, the IXZ631DF18N50 is suitable for higher power operation where combiners are used. Its features and wide safety margin in operating voltage and power make the IXZ631DF18N50 unmatched in performance and value.

The IXZ631DF18N50 is packaged in IXYSRF's low-inductance RF package incorporating layout techniques to minimize stray lead inductances for optimum switching performance. The IXZ631DF18N50 is a surface-mountable device.

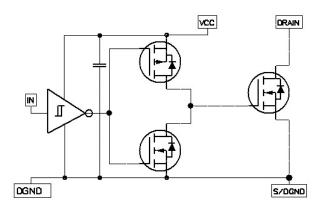

# Figure 1 Functional diagram

## **Device Specifications**

| Parameter                    | Value            |

|------------------------------|------------------|

| Maximum junction temperature | 150 °C           |

| Operating temperature range  | - 40 °C to 85 °C |

| Weight                       | 5.5 g            |

| Symbol                 | Test Conditions                 | Maximum Ratings |

|------------------------|---------------------------------|-----------------|

| <b>f</b> MAX           | ID = 0.5 IDM25 A                | 27 MHz          |

| VDSS                   |                                 | 500 V           |

| Vcc                    |                                 | 20 V            |

| Inna                   | VDS = 0.8 VDSS                  | 50 uA           |

| IDSS                   | VGS = 0 V $TJ = 125$ °C         | 1 mA            |

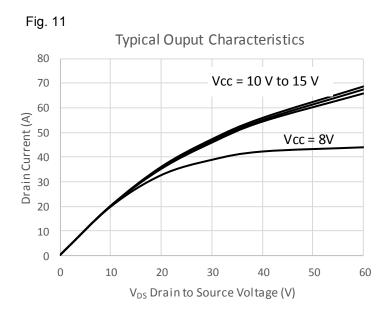

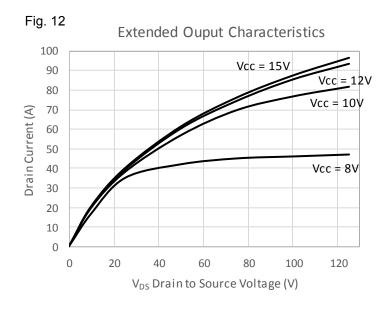

| IDM25                  | Tc = 25°C                       | 18 A            |

| IDM                    | Tc = 25°C, pulse limited by Тлм | 95 A            |

| IAR                    | Tc = 25°C                       | 18 A            |

| PT (MOSFET and Driver) | Tc = 25°C                       | 625 W           |

| RthJC                  |                                 | 0.2 °C/W        |

| RthJHS                 |                                 | 0.4 °C/W        |

## **Device Performance**

| Symbol                   | <b>Test Condition</b>                                                                                 | Minimum | Typical     | Maximum     |

|--------------------------|-------------------------------------------------------------------------------------------------------|---------|-------------|-------------|

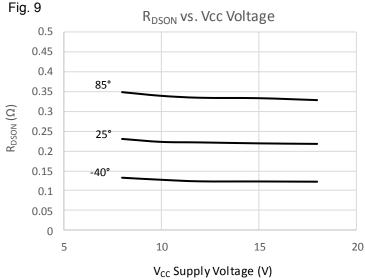

| RDS(ON)                  | $V_{CC}$ = 15 V, $I_D$ = 0.5 $I_{DM25}$ A<br>Pulse t ≤ 300 µs,<br>Duty Cycle ≤ 2%                     |         | 0.3 Ω       |             |

| <b>V</b> cc              |                                                                                                       | 8 V     | 15 V        | 20 V        |

| IN (Signal Input)        |                                                                                                       | - 5 V   |             | Vcc + 0.3 V |

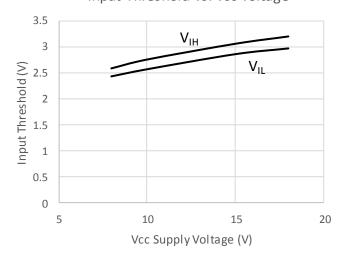

| VIH (High Input Voltage) | V <sub>CC</sub> = 15 V                                                                                | 3.5 V   | 3 V         |             |

| VIL (Low Input Voltage)  |                                                                                                       |         | 2.8 V       | 0.8 V       |

| VHYS (Input hysteresis)  |                                                                                                       |         | 0.23 V      |             |

| Zin                      | f = 1 MHz                                                                                             |         | 930-j7960 Ω |             |

| Cstray                   | f = 1 MHz any one pin to the<br>back plane metal                                                      |         | 46 pF       |             |

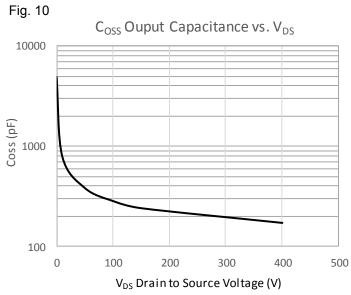

| Coss                     | $V_{IN}(V_{GS}) = 0 V$ , $V_{DS} = 0.8 V_{DSS(max)}$<br>f =1 MHz                                      |         | 172 pF      |             |

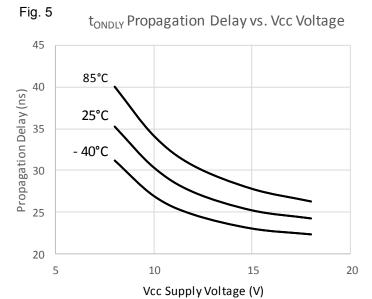

| tondly                   | $T_{C} = 25 ^{\circ}\text{C}$ $V_{CC} = 15 ^{\circ}\text{V}$ 1 µs pulse, $I_{D} = 9 ^{\circ}\text{A}$ |         | 25 ns       |             |

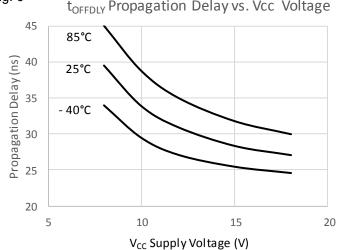

| <b>t</b> offdly          |                                                                                                       |         | 28 ns       |             |

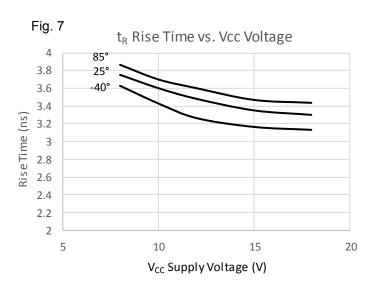

| tr                       |                                                                                                       |         | 3.4 ns      |             |

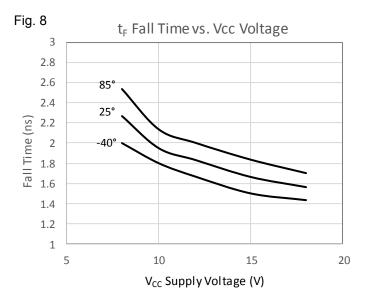

| tF                       |                                                                                                       |         | 1.65 ns     |             |

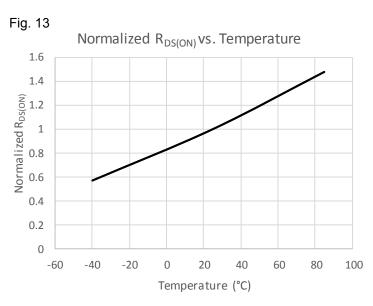

Fig. 2 Input Threshold vs. Vcc Voltage

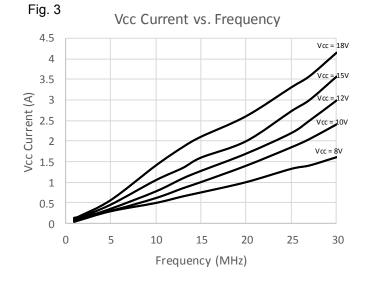

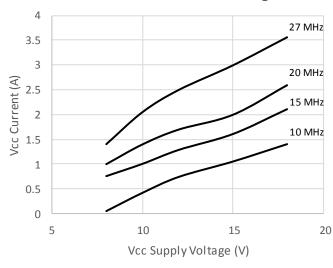

Fig. 4 Vcc Current vs. Vcc Voltage

Fig. 6  $t_{OFFDLY}$  Propagation Delay vs. Vcc Voltage

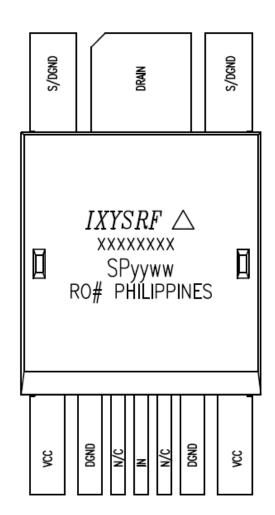

## **Lead description**

| SYMBOL | FUNCTION                      | DESCRIPTION                                                                                                                                                                                                      |

|--------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drain  | MOSFET drain                  | Drain of power MOSFET.                                                                                                                                                                                           |

| S/DGND | MOSFET source                 | Source of power MOSFET. This connection is common to DGND.                                                                                                                                                       |

| Vcc    | Driver section supply voltage | Power supply input for the logic input and driver output sections.                                                                                                                                               |

| IN     | Input                         | Input signal.                                                                                                                                                                                                    |

| DGND   | Driver power<br>ground        | The driver ground leads. Internally connected to all circuitry, these leads provide ground reference for the driver. These leads should be connected to a low-noise analog ground plane for optimum performance. |

| N/C    | None                          | No connection to this lead.                                                                                                                                                                                      |

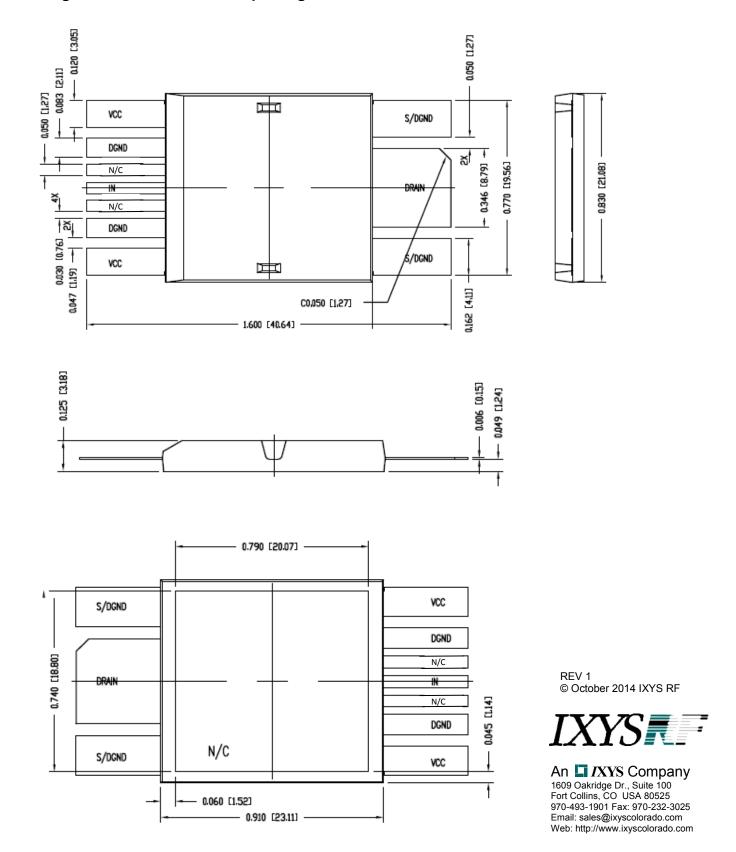

Figure 14 Package drawing

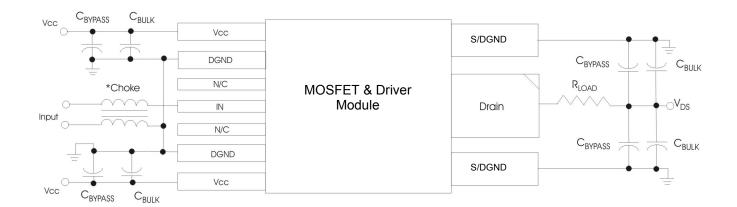

### Figure 15 Test circuit

\*Choke— A common-mode choke is optional and can be used to help stabilize the threshold level due to ground bounce and to minimize false triggering.

$C_{BULK}$ - Bulk capacitance helps to stabilize both the high voltage  $V_{DS}$  for the drain circuit and low voltage Vcc for the driver circuit. Actual values vary according to load and operating conditions. For the <u>driver</u> section, tantalum capacitors are recommended for their fast energy delivery.

$C_{BYPASS}$ - Ideally, the benefits realized through bypass capacitance increase as more is used by way of overlapping impedance curves, lowering the overall broadband impedance to ground. Typically a range of 0.1  $\mu$ F, 0.01  $\mu$ F, 0.001  $\mu$ F capacitors in sufficient quantities give good results.

Circuit board layout should be carefully considered to optimize operation. Each of the Vcc leads on the driver section should be treated as its own power supply lead. Bulk and bypass capacitors attached between drain and source leads should be placed symmetrically between the leads. Excessive parasitic inductance can result in V = L di/dt inductive voltage drops, causing unpredictable operation.

Figure 16 IXZ631DF18N50 package outline

IXYSRF reserves the right to change limits, test conditions, and dimensions without notice.