# **RMLV0816BGBG - 4S2**

8Mb Advanced LPSRAM (512k word × 16bit)

R10DS0229EJ0200 Rev.2.00 2015.06.26

### **Description**

The RMLV0816BGBG is a family of 8-Mbit static RAMs organized 524,288-word × 16-bit, fabricated by Renesas's high-performance Advanced LPSRAM technologies. The RMLV0816BGBG has realized higher density, higher performance and low power consumption. The RMLV0816BGBG offers low power standby power dissipation; therefore, it is suitable for battery backup systems. It is offered in 48-ball fine pitch ball grid array.

#### **Features**

- Single 3V supply: 2.4V to 3.6V

- Access time:

- Power supply voltage from 2.7V to 3.6V: 45ns (max.)

- Power supply voltage from 2.4V to 2.7V: 55ns (max.)

- Current consumption:

- Standby: 0.45μA (typ.)

- Equal access and cycle times

- Common data input and output

- Three state output

- Directly TTL compatible

- All inputs and outputs

- Battery backup operation

#### **Part Name Information**

| Part Name          | Power supply | Access time | Temperature<br>Range | Package                               |

|--------------------|--------------|-------------|----------------------|---------------------------------------|

| DMI V/0946DCDC 452 | 2.7V to 3.6V | 45 ns       | -40 ~ +85°C          | 48-ball FBGA with 0.75mm ball pitch   |

| RMLV0816BGBG-4S2   | 2.4V to 2.7V | 55 ns       | -40 ~ +65 C          | 40-ball FBGA With 0.75Hill ball pitch |

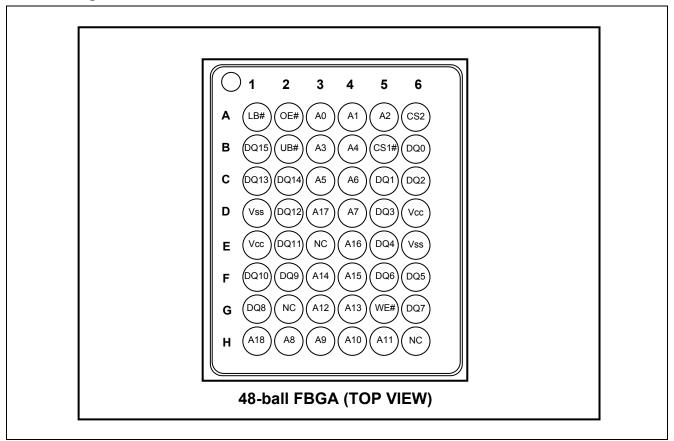

# **Pin Arrangement**

# **Pin Description**

| Pin name        | Function          |

|-----------------|-------------------|

| Vcc             | Power supply      |

| V <sub>SS</sub> | Ground            |

| A0 to A18       | Address input     |

| DQ0 to DQ15     | Data input/output |

| CS1#            | Chip select 1     |

| CS2             | Chip select 2     |

| OE#             | Output enable     |

| WE#             | Write enable      |

| LB#             | Lower byte select |

| UB#             | Upper byte select |

| NC              | No connection     |

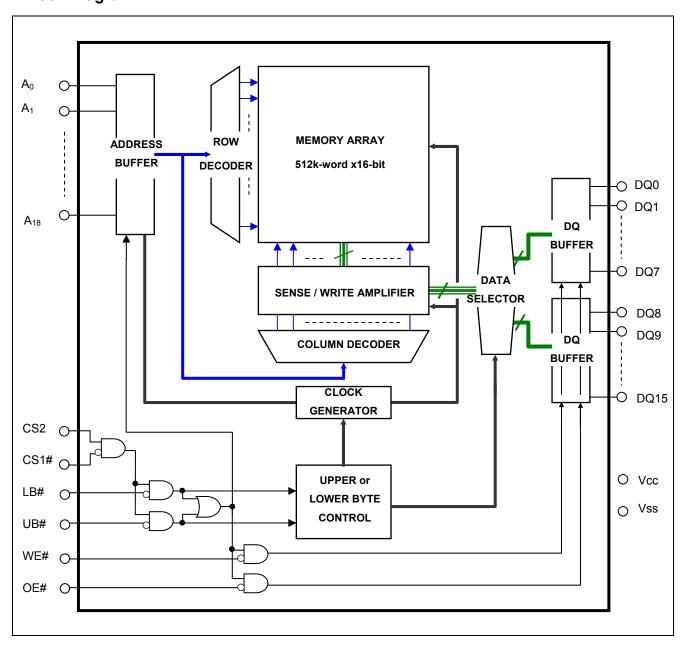

# **Block Diagram**

# **Operation Table**

| CS1# | CS2 | WE# | OE# | UB# | LB# | DQ0 to DQ7 | DQ8 to DQ15 | Operation        |

|------|-----|-----|-----|-----|-----|------------|-------------|------------------|

| Н    | Χ   | Χ   | Χ   | Χ   | Χ   | High-Z     | High-Z      | Standby          |

| Х    | L   | Х   | Х   | Х   | Х   | High-Z     | High-Z      | Standby          |

| Х    | Х   | Х   | Х   | Н   | Н   | High-Z     | High-Z      | Standby          |

| L    | Н   | Н   | L   | L   | L   | Dout       | Dout        | Read             |

| L    | Н   | Н   | L   | Н   | L   | Dout       | High-Z      | Lower byte read  |

| L    | Н   | Н   | L   | L   | Н   | High-Z     | Dout        | Upper byte read  |

| L    | Н   | L   | Х   | L   | L   | Din        | Din         | Write            |

| L    | Н   | L   | Х   | Н   | L   | Din        | High-Z      | Lower byte write |

| L    | Н   | L   | Х   | L   | Н   | High-Z     | Din         | Upper byte write |

| L    | Н   | Н   | Н   | Х   | Х   | High-Z     | High-Z      | Output disable   |

Note 1. H: V<sub>IH</sub> L:V<sub>IL</sub> X: V<sub>IH</sub> or V<sub>IL</sub>

### **Absolute Maximum Ratings**

| Parameter                                               | Symbol          | Value                                                    | unit |

|---------------------------------------------------------|-----------------|----------------------------------------------------------|------|

| Power supply voltage relative to V <sub>SS</sub>        | V <sub>CC</sub> | -0.5 to +4.6                                             | V    |

| Terminal voltage on any pin relative to V <sub>SS</sub> | V <sub>T</sub>  | -0.5 <sup>*2</sup> to V <sub>CC</sub> +0.3 <sup>*3</sup> | V    |

| Power dissipation                                       | P <sub>T</sub>  | 0.7                                                      | W    |

| Operation temperature                                   | Topr            | -40 to +85                                               | °C   |

| Storage temperature range                               | Tstg            | -65 to +150                                              | °C   |

| Storage temperature range under bias                    | Tbias           | -40 to +85                                               | °C   |

Note 2. -3.0V for pulse  $\leq 30$ ns (full width at half maximum)

3. Maximum voltage is +4.6V.

# **DC Operating Conditions**

| Parameter                 | Symbol          | Min. | Тур. | Max.                 | Unit | Test conditions  | Note |

|---------------------------|-----------------|------|------|----------------------|------|------------------|------|

| Supply voltage            | Vcc             | 2.4  | 3.0  | 3.6                  | V    |                  |      |

|                           | V <sub>SS</sub> | 0    | 0    | 0                    | V    |                  |      |

| Input high voltage        |                 | 2.0  | _    | V <sub>CC</sub> +0.2 | V    | Vcc=2.4V to 2.7V |      |

|                           | $V_{IH}$        | 2.2  | _    | V <sub>CC</sub> +0.2 | V    | Vcc=2.7V to 3.6V |      |

| Input low voltage         | V <sub>IL</sub> | -0.2 | _    | 0.4                  | V    | Vcc=2.4V to 2.7V | 4    |

|                           |                 | -0.2 | _    | 0.6                  | V    | Vcc=2.7V to 3.6V | 4    |

| Ambient temperature range | Та              | -40  | _    | +85                  | °C   |                  |      |

Note 4. -3.0V for pulse  $\leq 30$ ns (full width at half maximum)

#### **DC Characteristics**

| Parameter                 | Symbol           | Min. | Тур.              | Max. | Unit | Test conditions                                                                                                                                                                                              |    |  |

|---------------------------|------------------|------|-------------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| Input leakage current     | I <sub>LI</sub>  | _    | _                 | 1    | μА   | Vin = V <sub>SS</sub> to V <sub>CC</sub>                                                                                                                                                                     |    |  |

| Output leakage current    | I <sub>LO</sub>  | _    | _                 | 1    | μΑ   | $ \begin{aligned} &CS1\# = V_{IH} \text{ or } CS2 = V_{IL} \text{ or } OE\# = V_{IH} \\ &\text{ or } WE\# = V_{IL} \text{ or } LB\# = UB\# = V_{IH}, \\ &V_{I/O} = V_{SS} \text{ to } V_{CC} \end{aligned} $ |    |  |

| Average operating current |                  | -    | 20 <sup>*5</sup>  | 25   | mA   | Cycle = 55ns, duty =100%, $I_{I/O}$ = 0mA, CS1# = $V_{IL}$ , CS2 = $V_{IH}$ , Others = $V_{IH}/V_{IL}$                                                                                                       |    |  |

|                           | I <sub>CC1</sub> | ı    | 25 <sup>*5</sup>  | 30   | mA   | Cycle = 45ns, duty =100%, $I_{I/O}$ = 0mA,<br>CS1# = $V_{IL}$ , CS2 = $V_{IH}$ , Others = $V_{IH}/V_{IL}$                                                                                                    |    |  |

|                           | I <sub>CC2</sub> | _    | 1.5 <sup>*5</sup> | 3    | mA   | Cycle = 1 $\mu$ s, duty =100%, I <sub>I/O</sub> = 0mA,<br>CS1# $\leq$ 0.2V, CS2 $\geq$ V <sub>CC</sub> -0.2V,<br>V <sub>IH</sub> $\geq$ V <sub>CC</sub> -0.2V, V <sub>IL</sub> $\leq$ 0.2V                   |    |  |

| Standby current           | I <sub>SB</sub>  | _    | _                 | 0.3  | mA   | CS2 = V <sub>IL</sub> , Others = V <sub>SS</sub> to V <sub>CC</sub>                                                                                                                                          |    |  |

| Standby current           |                  | -    | 0.45*5            | 2    | μА   | ~+25°C $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                |    |  |

|                           | I <sub>SB1</sub> | _    | 0.6*6             | 4    | μΑ   | ~+40°C or<br>(2) CS1# ≥ V <sub>CC</sub> -0.2V,                                                                                                                                                               |    |  |

|                           |                  | _    | _                 | 7    | μА   | ~+70°C CS2 ≥ V <sub>CC</sub> -0.2V or                                                                                                                                                                        |    |  |

|                           |                  | _    | _                 | 10   | μΑ   | ~+85°C (3) LB# = UB# ≥ V <sub>CC</sub> -0.2V,<br>CS1# ≤ 0.2V, CS2 ≥ V <sub>CC</sub> -0.2                                                                                                                     | 2V |  |

| Output high voltage       | V <sub>OH</sub>  | 2.4  | _                 | _    | ٧    | I <sub>OH</sub> = -1mA<br>Vcc≥2.7V<br>I <sub>OH</sub> = -0.1mA                                                                                                                                               |    |  |

|                           | V <sub>OH2</sub> | 2.0  | _                 | _    | V    |                                                                                                                                                                                                              |    |  |

| Output low voltage        | V <sub>OL</sub>  | _    | _                 | 0.4  | V    | I <sub>OL</sub> = 2mA<br>Vcc≥2.7V                                                                                                                                                                            |    |  |

|                           | V <sub>OL2</sub> | _    | _                 | 0.4  | V    | I <sub>OL</sub> = 0.1mA                                                                                                                                                                                      |    |  |

Note 5. Typical parameter indicates the value for the center of distribution at 3.0V (Ta=25°C), and not 100% tested.

Note 6. Typical parameter indicates the value for the center of distribution at 3.0V (Ta=40°C), and not 100% tested.

### Capacitance

(Ta = $25^{\circ}$ C, f =1MHz)

| Parameter                  | Symbol           | Min. | Тур. | Max. | Unit | Test conditions      | Note |

|----------------------------|------------------|------|------|------|------|----------------------|------|

| Input capacitance          | C in             | _    | _    | 8    | pF   | Vin =0V              | 7    |

| Input / output capacitance | C <sub>I/O</sub> | _    | _    | 10   | pF   | V <sub>I/O</sub> =0V | 7    |

Note 7. This parameter is sampled and not 100% tested.

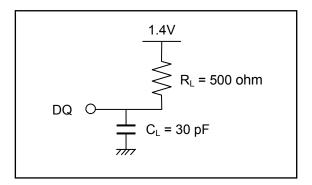

#### **AC Characteristics**

Test Conditions (Vcc =  $2.4V \sim 3.6V$ , Ta =  $-40 \sim +85$ °C)

• Input pulse levels:

$$V_{IL} = 0.4V$$

,  $V_{IH} = 2.4V$  (Vcc=2.7V to 3.6V)

$V_{IL} = 0.4V$ ,  $V_{IH} = 2.2V$  (Vcc=2.4V to 2.7V)

- Input rise and fall time: 5ns

- Input and output timing reference level: 1.4V

- Output load: See figures (Including scope and jig)

#### **Read Cycle**

| Darameter                          | Cumbal            | Vcc=2.7 | V to 3.6V | Vcc=2.4 | V to 2.7V | Unit | Note   |

|------------------------------------|-------------------|---------|-----------|---------|-----------|------|--------|

| Parameter                          | Symbol            | Min.    | Max.      | Min.    | Max.      | Unit | Note   |

| Read cycle time                    | t <sub>RC</sub>   | 45      | _         | 55      | _         | ns   |        |

| Address access time                | t <sub>AA</sub>   | _       | 45        | _       | 55        | ns   |        |

| Chin coloct access time            | t <sub>ACS1</sub> | _       | 45        | _       | 55        | ns   |        |

| Chip select access time            | t <sub>ACS2</sub> | _       | 45        | _       | 55        | ns   |        |

| Output enable to output valid      | t <sub>OE</sub>   | _       | 22        | _       | 30        | ns   |        |

| Output hold from address change    | t <sub>OH</sub>   | 10      | _         | 10      | _         | ns   |        |

| LB#, UB# access time               | t <sub>BA</sub>   | _       | 45        | _       | 55        | ns   |        |

| Chin coloct to output in low 7     | t <sub>CLZ1</sub> | 10      | _         | 10      | _         | ns   | 8,9    |

| Chip select to output in low-Z     | t <sub>CLZ2</sub> | 10      | _         | 10      | _         | ns   | 8,9    |

| LB#, UB# enable to low-Z           | t <sub>BLZ</sub>  | 5       | _         | 5       | _         | ns   | 8,9    |

| Output enable to output in low-Z   | t <sub>OLZ</sub>  | 5       | _         | 5       | _         | ns   | 8,9    |

| Chin deceler to output in high 7   | t <sub>CHZ1</sub> | 0       | 18        | 0       | 20        | ns   | 8,9,10 |

| Chip deselect to output in high-Z  | t <sub>CHZ2</sub> | 0       | 18        | 0       | 20        | ns   | 8,9,10 |

| LB#, UB# disable to high-Z         | t <sub>BHZ</sub>  | 0       | 18        | 0       | 20        | ns   | 8,9,10 |

| Output disable to output in high-Z | t <sub>OHZ</sub>  | 0       | 18        | 0       | 20        | ns   | 8,9,10 |

Note 8. This parameter is sampled and not 100% tested.

- 9. At any given temperature and voltage condition,  $t_{CHZ1}$  max is less than  $t_{CLZ1}$  min,  $t_{CHZ2}$  max is less than  $t_{CLZ2}$  min,  $t_{BHZ}$  max is less than  $t_{BLZ}$  min, and  $t_{OHZ}$  max is less than  $t_{OLZ}$  min, for any device.

- 10.  $t_{CHZ1}$ ,  $t_{CHZ2}$ ,  $t_{BHZ}$  and  $t_{OHZ}$  are defined as the time when the DQ pins enter a high-impedance state and are not referred to the DQ levels.

### **Write Cycle**

| Parameter                                          | Cumbal           | Vcc=2.7 | V to 3.6V | Vcc=2.4 | V to 2.7V | Unit | Note  |

|----------------------------------------------------|------------------|---------|-----------|---------|-----------|------|-------|

| Parameter                                          | Symbol           | Min.    | Max.      | Min.    | Max.      | Unit | Note  |

| Write cycle time                                   | twc              | 45      | _         | 55      | _         | ns   |       |

| Address valid to write end                         | t <sub>AW</sub>  | 35      | _         | 50      | _         | ns   |       |

| Chip select to write end                           | t <sub>CW</sub>  | 35      | _         | 50      | _         | ns   |       |

| Write pulse width                                  | t <sub>WP</sub>  | 35      | _         | 40      | _         | ns   | 11    |

| LB#,UB# valid to write end                         | t <sub>BW</sub>  | 35      | _         | 50      | _         | ns   |       |

| Address setup time to write start                  | t <sub>AS</sub>  | 0       | _         | 0       | _         | ns   |       |

| Write recovery time from write end                 | t <sub>WR</sub>  | 0       | _         | 0       | _         | ns   |       |

| Data to write time overlap                         | t <sub>DW</sub>  | 25      | _         | 25      | _         | ns   |       |

| Data hold from write end                           | t <sub>DH</sub>  | 0       | _         | 0       | _         | ns   |       |

| Output enable from write end                       | tow              | 5       | _         | 5       | _         | ns   | 12    |

| Output disable to output in high-Z t <sub>OH</sub> |                  | 0       | 18        | 0       | 20        | ns   | 12,13 |

| Write to output in high-Z                          | t <sub>WHZ</sub> | 0       | 18        | 0       | 20        | ns   | 12,13 |

Note 11.  $t_{WP}$  is the interval between write start and write end.

A write starts when all of (CS1#), (CS2), (WE#) and (one or both of LB# and UB#) become active. A write is performed during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#. A write ends when any of (CS1#), (CS2), (WE#) or (one or both of LB# and UB#) becomes inactive.

- 12. This parameter is sampled and not 100% tested.

- 13.  $t_{OHZ}$  and  $t_{WHZ}$  are defined as the time when the DQ pins enter a high-impedance state and are not referred to the DQ levels.

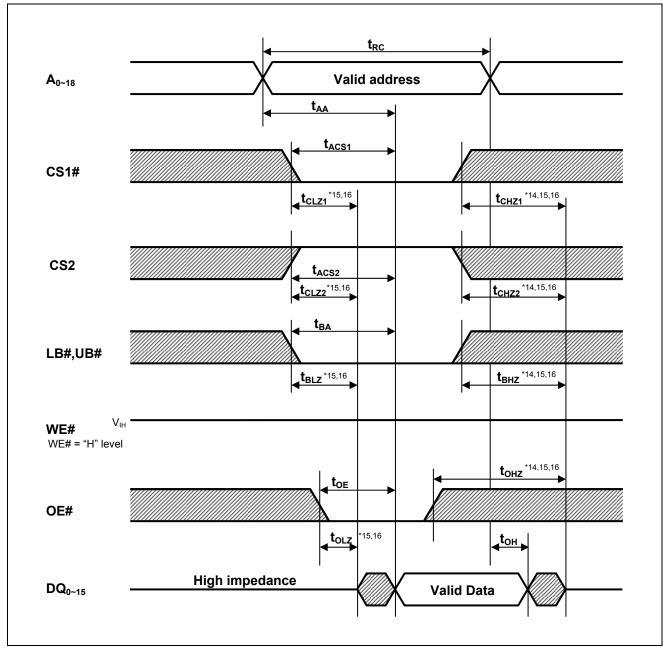

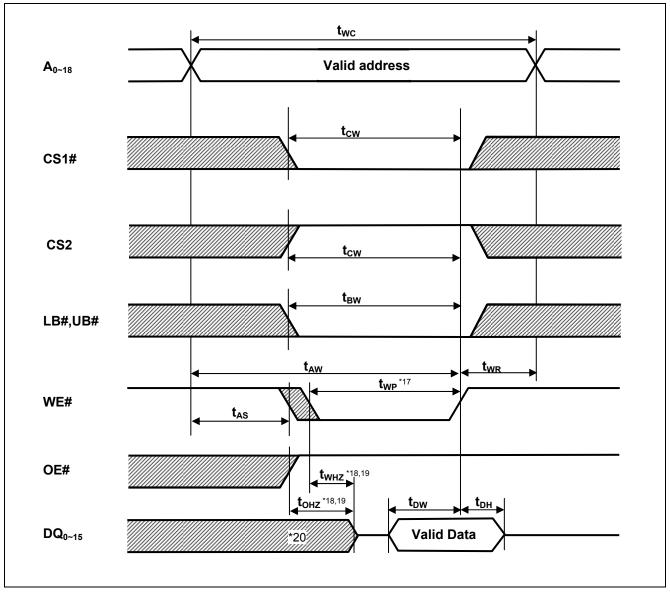

### **Timing Waveforms**

#### **Read Cycle**

Note 14.  $t_{CHZ1}$ ,  $t_{CHZ2}$ ,  $t_{BHZ}$  and  $t_{OHZ}$  are defined as the time when the DQ pins enter a high-impedance state and are not referred to the DQ levels.

- 15. This parameter is sampled and not 100% tested

- 16. At any given temperature and voltage condition,  $t_{CHZ1}$  max is less than  $t_{CLZ1}$  min,  $t_{CHZ2}$  max is less than  $t_{CLZ}$  min,  $t_{BHZ}$  max is less than  $t_{BLZ}$  min, and  $t_{OHZ}$  max is less than  $t_{OLZ}$  min, for any device.

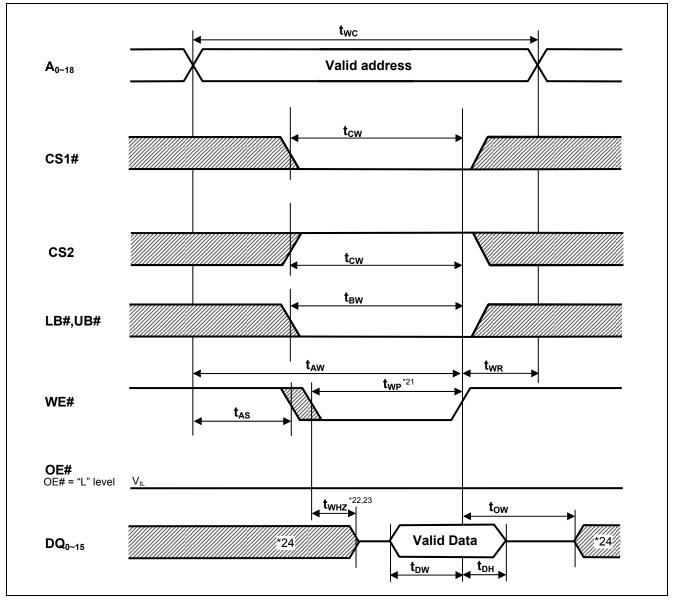

### Write Cycle (1) (WE# CLOCK, OE#="H" while writing)

Note 17. twp is the interval between write start and write end.

A write starts when all of (CS1#), (CS2), (WE#) and (one or both of LB# and UB#) become active.

A write is performed during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#.

A write ends when any of (CS1#), (CS2), (WE#) or (one or both of LB# and UB#) becomes inactive.

- 18. t<sub>OHZ</sub> and t<sub>WHZ</sub> are defined as the time when the DQ pins enter a high-impedance state and are not referred to the DQ levels.

- 19. This parameter is sampled and not 100% tested

- 20. During this period, DQ pins are in the output state so input signals must not be applied to the DQ pins.

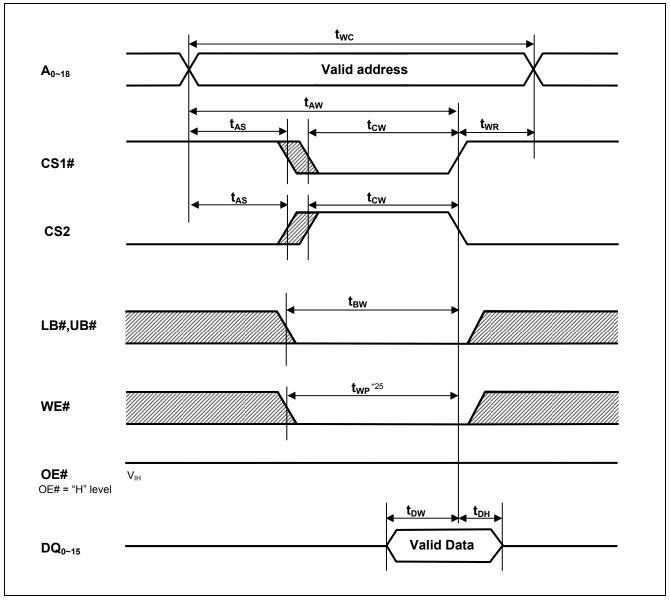

#### Write Cycle (2) (WE# CLOCK, OE# Low Fixed)

Note 21. twp is the interval between write start and write end.

A write starts when all of (CS1#), (CS2), (WE#) and (one or both of LB# and UB#) become active.

A write is performed during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#.

A write ends when any of (CS1#), (CS2), (WE#) or (one or both of LB# and UB#) becomes inactive.

- 22.  $t_{WHZ}$  is defined as the time when the DQ pins enter a high-impedance state and are not referred to the DQ levels.

- 23. This parameter is sampled and not 100% tested.

- 24. During this period, DQ pins are in the output state so input signals must not be applied to the DQ pins.

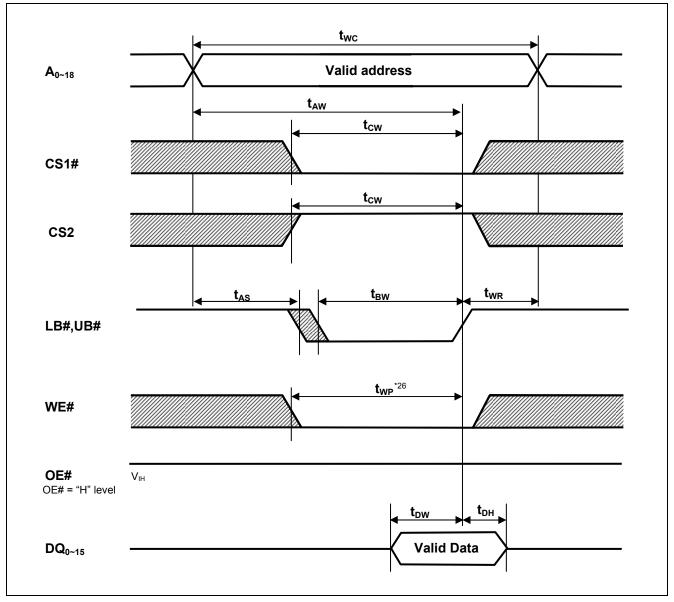

### Write Cycle (3) (CS1#, CS2 CLOCK)

Note 25. twp is the interval between write start and write end.

A write starts when all of (CS1#), (CS2), (WE#) and (one or both of LB# and UB#) become active.

A write is performed during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#.

A write ends when any of (CS1#), (CS2), (WE#) or (one or both of LB# and UB#) becomes inactive.

### Write Cycle (4) (LB#, UB# CLOCK)

Note 26. twp is the interval between write start and write end.

A write starts when all of (CS1#), (CS2), (WE#) and (one or both of LB# and UB#) become active. A write is performed during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#. A write ends when any of (CS1#), (CS2), (WE#) or (one or both of LB# and UB#) becomes inactive.

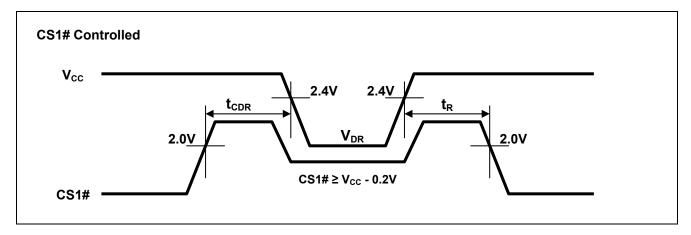

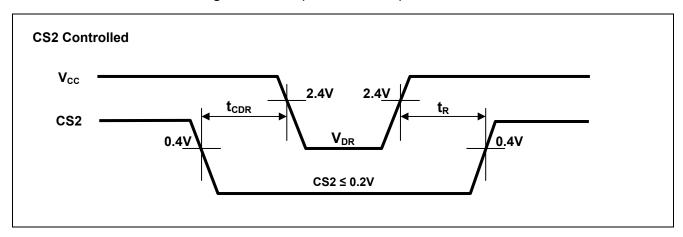

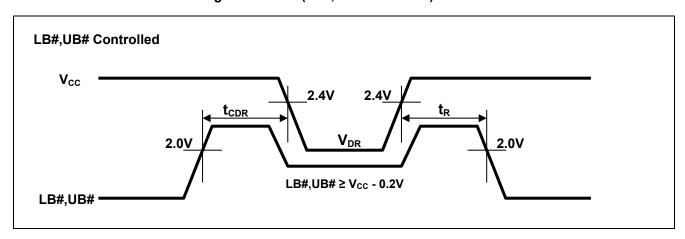

### Low V<sub>CC</sub> Data Retention Characteristics

| Parameter                            | Symbol           | Min. | Тур.                | Max. | Unit |                         | Test conditions*29                                                                                                                                           |  |

|--------------------------------------|------------------|------|---------------------|------|------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC</sub> for data retention   | V <sub>DR</sub>  | 1.5  | _                   | 3.6  | V    | or<br>(3) LB# =         | 0.2V<br>$\geq$ V <sub>CC</sub> -0.2V, CS2 $\geq$ V <sub>CC</sub> -0.2V<br>UB# $\geq$ V <sub>CC</sub> -0.2V,<br>$\leq$ 0.2V, CS2 $\geq$ V <sub>CC</sub> -0.2V |  |

|                                      | Iccdr            | _    | 0.45 <sup>*27</sup> | 2    | μΑ   | ~+25°C                  | V <sub>CC</sub> = 3.0V, Vin ≥ 0V,<br>(1) CS2 ≤ 0.2V                                                                                                          |  |

| Data retention current               |                  | _    | 0.6 <sup>*28</sup>  | 4    | μΑ   | ~+40°C                  | or<br>(2) CS1# ≥ V <sub>CC</sub> -0.2V,<br>CS2 ≥ V <sub>CC</sub> -0.2V                                                                                       |  |

| Data retention current               |                  | _    | _                   | 7    | μΑ   | ~+70°C                  | or<br>(3) LB# = UB# ≥ V <sub>CC</sub> -0.2V,                                                                                                                 |  |

|                                      |                  | _    | _                   | 10   | μΑ   | ~+85°C                  | CS1# ≤ 0.2V,<br>CS2 ≥ V <sub>CC</sub> -0.2V                                                                                                                  |  |

| Chip deselect time to data retention | t <sub>CDR</sub> | 0    | _                   | _    | ns   | See reton               | tion waveform                                                                                                                                                |  |

| Operation recovery time              | t <sub>R</sub>   | 5    | _                   | _    | ms   | See retention waveform. |                                                                                                                                                              |  |

- Note 27. Typical parameter indicates the value for the center of distribution at 3.0V (Ta=25°C), and not 100% tested.

- 28. Typical parameter indicates the value for the center of distribution at 3.0V (Ta=40°C), and not 100% tested.

- 29. CS2 controls address buffer, WE# buffer, CS1# buffer, OE# buffer, LB# buffer, UB# buffer and DQ buffer. If CS2 controls data retention mode, Vin levels (address, WE#, CS1#, OE#, LB#, UB#, DQ) can be in the high impedance state. If CS1# controls data retention mode, CS2 must be CS2 ≥ V<sub>CC</sub>-0.2V or CS2 ≤ 0.2V. The other inputs levels (address, WE#, OE#, LB#, UB#, DQ) can be in the high-impedance state.

### Low Vcc Data Retention Timing Waveforms (CS1# controlled)

#### Low Vcc Data Retention Timing Waveforms (CS2 controlled)

### Low Vcc Data Retention Timing Waveforms (LB#,UB# controlled)

Revision History

# RMLV0816BGBG Data Sheet

|      |            | Description |                                                                                                |  |  |  |  |  |

|------|------------|-------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Rev. | Date       | Page        | Summary                                                                                        |  |  |  |  |  |

| 1.00 | 2014.11.28 | _           | First Edition issued                                                                           |  |  |  |  |  |

| 2.00 | 2015.06.26 | P.1, 4      | Standby current I <sub>SB1</sub> : 25°C 0.6μA ->0.45μA (typ.), 40°C 2μA ->0.6μA (typ.)         |  |  |  |  |  |

|      |            | P.4         | Average operating current I <sub>CC2</sub> : 25°C 2mA ->1.5mA (typ.)                           |  |  |  |  |  |

|      |            | P.12        | Data retention current I <sub>CCDR</sub> : 25°C 0.6μA ->0.45μA (typ.), 40°C 2μA ->0.6μA (typ.) |  |  |  |  |  |

|      |            |             |                                                                                                |  |  |  |  |  |

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

#### **SALES OFFICES**

#### Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 2801 Scott Boulevard Santa Clara, CA 95050-2549, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-585-100, Fax: +44-1628-585-900

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China Tel: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333

Tel: 486-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2865-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 TE: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tei: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd.

No.777C, 100 Feet Road, HALII Stage, Indiranagar, Bangalore, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd. 12F., 234 Teheran-ro, Gangnam-Gu, Seoul, 135-080, Korea Tel: +82-2-558-3737, Fax: +82-2-558-5141