# Low Voltage 1:4 CMOS Clock Buffer

MPC94551

#### PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES SEPTEMBER 7, 2016

**DATASHEET**

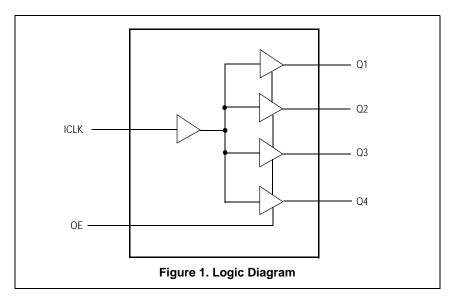

The MPC94551 is a CMOS 1:4 fanout buffer. The MPC94551 is ideal for applications requiring lower voltage.

#### **Features**

- 1:4 CMOS fanout buffer

- 300 ps output to output skew

- I/O frequency up to 160 MHz operation

- Non-inverting output clock

- 3.3 V supply voltage

- Output Enable mode tri-states outputs

- -40°C to 85°C industrial temperature range

- 8-lead SOIC package, Pb-free

- For drop in replacement use 551MI

### MPC94551

1:4 LVCMOS CLOCK BUFFER

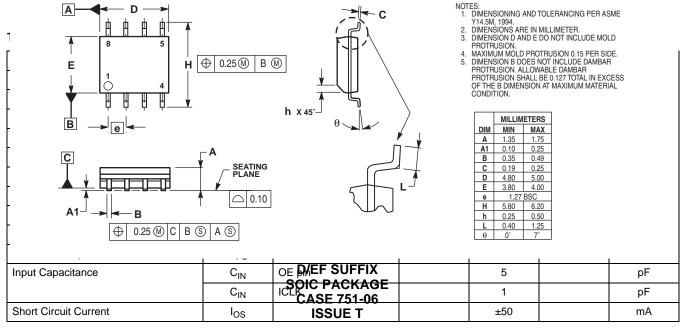

EF SUFFIX 8-LEAD SOIC PACKAGE Pb-FREE PACKAGE CASE 751-06

| ORDERING INFORMATION |                |  |  |  |

|----------------------|----------------|--|--|--|

| Device               | Package        |  |  |  |

| MPC94551EF           | SO-8 (Pb-FREE) |  |  |  |

| MPC94551EFR2         | SO-8 (Pb-FREE) |  |  |  |

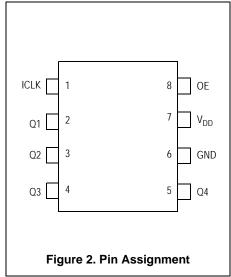

**Table 1. Pin Description**

| Pin Number | Pin Name        | Pin Type | Pin Description                                                       |

|------------|-----------------|----------|-----------------------------------------------------------------------|

| 1          | ICLK            | Input    | Clock input, internal pull-up resistor                                |

| 2          | Q1              | Output   | Clock output <sup>(1)</sup>                                           |

| 3          | Q2              | Output   | Clock output <sup>(1)</sup>                                           |

| 4          | Q3              | Output   | Clock output <sup>(1)</sup>                                           |

| 5          | Q4              | Output   | Clock output <sup>(1)</sup>                                           |

| 6          | GND             | Power    | Connect to ground <sup>(2)</sup>                                      |

| 7          | V <sub>DD</sub> | Power    | Connect to 3.3 V <sup>(2)</sup>                                       |

| 8          | OE              | Input    | Output enable, tri-states outputs when low, internal pull-up resistor |

- 1. A 33  $\Omega$  series terminating resistor may be used on each clock output if the trace is longer than 1 inch.

- 2. A decoupling capacitor of 0.01  $\mu$ F should be connected between  $V_{DD}$  on pin 7 and GND on pin 6, as close to the device as possible.

Table 2. Absolute Maximum Ratings<sup>(1)</sup>

| Parameter                             | Rating                       | Unit |

|---------------------------------------|------------------------------|------|

| Power Supply Voltage, V <sub>DD</sub> | 3.9                          | V    |

| All Inputs and Outputs                | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Ambient Operating Temperature         | -40 to +85                   | °C   |

| Storage Temperature                   | -65 to +150                  | °C   |

| Junction Temperature                  | 175                          | °C   |

| Soldering Temperature                 | 260                          | °C   |

1. Stresses above the ratings listed below can cause permanent damage to the device. These ratings are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied.

1. Nominal switching threshold is  $V_{DD}/2$ .

Table 4. AC Characteristics ( $V_{DD}$  = 3.3 V ± 5%; Ambient Temperature = -40°C to 85°C)

| Parameter                            | Symbol          | Condition                          | Min | Тур | Max | Unit |

|--------------------------------------|-----------------|------------------------------------|-----|-----|-----|------|

| Input Frequency                      |                 |                                    | 0   |     | 160 | MHz  |

| Output Frequency <sup>(1)</sup>      |                 | 15 pF load                         |     |     | 160 | MHz  |

| Output Clock Rise Time               | t <sub>OR</sub> | 0.8 V to 2.0 V                     |     |     | 1.5 | ns   |

| Output Clock Fall Time               | t <sub>OF</sub> | 2.0 V to 0.8 V                     |     |     | 1.5 | ns   |

| Propagation Delay <sup>(2)</sup>     |                 | 135 MHz                            | 1.5 | 4   | 5   | ns   |

| Output to Output Skew <sup>(3)</sup> |                 | Rising edges at V <sub>DD</sub> /2 |     |     | 300 | ps   |

- 1. Measured with an external series resistor of  $33\Omega$  positioned close to each output pin

- 2. Measured with rail to rail input clock

- 3. Measured between any 2 outputs with equal loading

### **Revision History Sheet**

| Rev | Table | Page | Description of Change                                                                 | Date     |

|-----|-------|------|---------------------------------------------------------------------------------------|----------|

| 4   |       | 1    | NRND – Not Recommend for New Designs                                                  | 12/21/12 |

| 4   |       | 1    | Removed NRND                                                                          | 5/5/15   |

| 4   |       | 1    | Product Discontinuation Notice - Last time buy expires September 7, 2016. PDN N-16-02 | 3/15/16  |

## We've Got Your Timing Solution

6024 Silver Creek Valley Road San Jose, California 95138 Sales

800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT Technical Support

clocks@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT's products for any particular purpose.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third

©2016 Integrated Device Technology, Inc. All rights reserved.