### ISL21440

Micropower Voltage Reference with Comparator

FN6532 Rev.4.00 Mar 24, 2017

The <u>ISL21440</u> is a micropower, FGA reference, and comparator on a single chip. Drawing less than  $5\mu A$  supply current across the full operating temperature range, the ISL21440 operates from a single 2V to 11V supply and can also be used with split bipolar supplies.

The ISL21440's on-board reference provides a  $1.182V \pm 0.5\%$  output. It features programmable hysteresis and TTL/CMOS compatible outputs that sink and source current. Low bias currents permit high value divider resistors for typical circuit current drains of <2.5µA.

The low supply current makes the ISL21440 ideal for battery powered devices in battery level or low voltage monitor circuits.

The ISL21440 is a pin-compatible, performance upgrade of the LTC1440, LTC1540, MAX921, and MAX931.

### **Features**

- 5µA supply current across full temperature range

- Precision 1.182V ±0.5% voltage reference

- · Comparator with user programmable hysteresis

- Temperature range .....-40°C to +125°C

- 8 Ld MSOP and 8 Ld TDFN packages

- Pin compatible upgrade to MAX921 and LTC1440

### **Applications**

- · Low battery detector

- · Low voltage reset

- · Overvoltage monitor

- · Window comparator

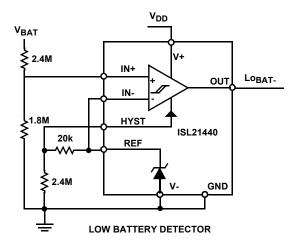

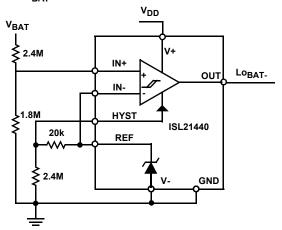

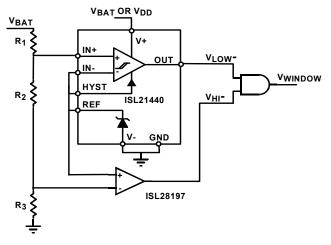

FIGURE 1. TYPICAL APPLICATION

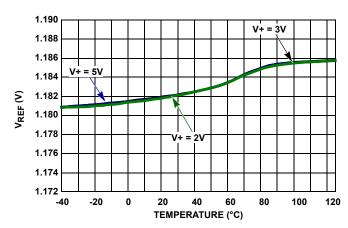

FIGURE 2. REFERENCE VOLTAGE vs TEMPERATURE

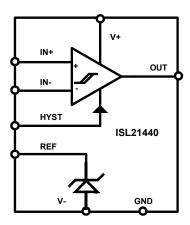

### **Block Diagram**

FIGURE 3. BLOCK DIAGRAM

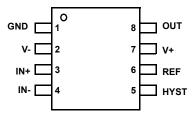

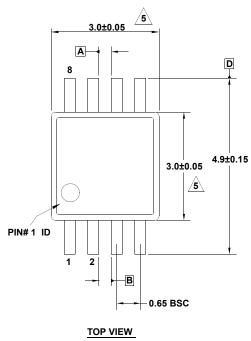

### **Pin Configuration**

ISL21440 (8 LD MSOP, 8 LD TDFN) TOP VIEW

## **Pin Descriptions**

| PIN                                                  | SYMBOL                                                        | DESCRIPTION                                                                                                                                                                   |

|------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                    | GND                                                           | Ground pin. Sets the comparator output low level.                                                                                                                             |

| 2                                                    | V-                                                            | Negative supply input for voltage reference and comparator.                                                                                                                   |

| 3                                                    | IN+ Comparator noninverting input pin. Range: V- to V+ -1.5V. |                                                                                                                                                                               |

| 4                                                    | IN-                                                           | Comparator inverting input pin. Range: V- to V+ -1.5V.                                                                                                                        |

| from the reference output. Range is V <sub>REF</sub> |                                                               | Comparator hysteresis input. Accepts a voltage divided from the reference output. Range is $V_{REF}$ - 50mV to $V_{REF}$ . Connect directly to $V_{REF}$ for zero hysteresis. |

| 6                                                    | REF                                                           | Reference output. Source 2mA and Sink 10μA.                                                                                                                                   |

| 7                                                    | V+                                                            | Positive supply input for comparator and reference.<br>Range is 2.0V to 11.0V                                                                                                 |

| 8                                                    | OUT                                                           | Comparator output, CMOS push-pull. Output swing referenced to V+ and GND.                                                                                                     |

## **Ordering Information**

| PART NUMBER<br>(Notes 3, 4)    | PART MARKING | V <sub>DD</sub> RANGE<br>(V) | TEMP RANGE<br>(°C) | PACKAGE<br>(RoHS COMPLIANT) | PKG.<br>DWG. # |

|--------------------------------|--------------|------------------------------|--------------------|-----------------------------|----------------|

| ISL21440IRTZ ( <u>Note 1</u> ) | 1440         | 2 to 11                      | -40 to +125        | 8 Ld TDFN                   | L8.3x3G        |

| ISL21440IUZ ( <u>Note 2</u> )  | 1440Z        | 2 to 11                      | -40 to +125        | 8 Ld MSOP                   | M8.118         |

#### NOTES:

- 1. Add "-T13" suffix for 6k unit tape and reel option. Refer to TB347 for details on reel specifications.

- 2. Add "-T13" suffix for 2.5k unit tape and reel option. Refer to TB347 for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), see device information page for <a href="ISL21440">ISL21440</a>. For more information on MSL, see techbrief <a href="IB363">IB363</a>.

### **Absolute Maximum Ratings**

| Supply Voltage Range, V+ to GND                  |                            |

|--------------------------------------------------|----------------------------|

| GND with Respect to V                            | 6.0V to -0.3V              |

| V+ with Respect to V                             | 12V to -0.3V               |

| REF, HYST with Respect to V                      | 0.3V to 1.5V               |

| Out with Respect to GND                          | (V+) +0.3V to -0.3V        |

| Voltage on All Other Pins                        | $-0.3V$ to $V_{CC} + 0.3V$ |

| ESD Rating                                       |                            |

| Human Body Model                                 | 4kV                        |

| Machine Model                                    | 350V                       |

| Charged Device Model                             | 2kV                        |

| Latch-Up (Tested Per JESD-78B; Class 1, Level A) | 100mA                      |

### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}(^{\circ}C/W)$ | $\theta_{JC}$ (°C/W) |

|-------------------------------------------|----------------------------|----------------------|

| 8 Ld MSOP Package (Notes 6, 8)            | 154                        | 55                   |

| 8 Ld TDFN Package (Notes 6, 7)            | 68                         | 8                    |

| Maximum Junction Temperature (Plastic Pac | kage)                      | +150°C               |

| Storage Temperature Range                 | 6!                         | 5°C to +150°C        |

| Pb-Free Reflow Profile (Note 9)           |                            | see <u>TB493</u>     |

### **Recommended Operating Conditions**

| Temperature    | )°C to +125°C |

|----------------|---------------|

| Supply Voltage | 2.7V to 5.5V  |

### **Environmental Operating Conditions**

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5. Measured with no filtering, distance of 10" from source, intensity set to 55kV and 70mA current, 30s duration. Other exposure levels should be analyzed for output voltage drift effects. See "Applications Information" on page 10.

- 6.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See tech brief TB379 for details.

- 7. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 8. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

- 9. Post-reflow drift for the ISL21440 device voltage reference output will range from 100mV to 1.0mV based on experimental results with devices on FR4 double sided boards. The design engineer must take this into account when considering the reference voltage after assembly.

## **Analog Specifications (V+ = +5.0V)** V- = GND = 0V unless otherwise specified, T<sub>A</sub> = +25°C. **Boldface limits apply across the operating temperature range, -40°C to +125°C.**

| SYMBOL          | PARAMETER                              | TEST C                     | MIN<br>( <u>Note 11</u> ) | TYP ( <u>Note 10</u> ) | MAX<br>( <u>Note 11</u> ) | UNIT       |      |

|-----------------|----------------------------------------|----------------------------|---------------------------|------------------------|---------------------------|------------|------|

| POWER SU        | PPLY                                   | -                          |                           | '                      | '                         |            |      |

| V <sub>+</sub>  | Supply Voltage Range                   | V- = GND                   |                           | 2.0                    |                           | 11.0       | V    |

| Icc             | Supply Current                         | IN+ = IN- +80mV, HY        | ST = REF                  |                        | 0.46                      | 0.75       | μΑ   |

|                 |                                        |                            |                           |                        |                           | 5          | μΑ   |

| COMPARAT        | OR                                     | "                          |                           | <u>'</u>               |                           |            |      |

| Vos             | Input Offset Voltage                   | V <sub>CM</sub> = 2.5V     | MSOP Package              |                        |                           | ±3         | mV   |

|                 |                                        |                            | TDFN Package              |                        | ±3.25                     | mV         |      |

|                 |                                        |                            |                           |                        |                           | ±3.6       | mV   |

|                 |                                        |                            |                           |                        |                           | ±3.75      | mV   |

| IIN             | Input Leakage Current (IN+, IN-, HYST) | $V_{IN+} = V_{IN-} = 2.5V$ | MSOP Package              |                        | 0.1                       | 1.4        | nA   |

|                 |                                        |                            | TDFN Package              |                        | 0.1                       | 1.5        | nA   |

|                 |                                        |                            |                           |                        |                           | 3          | nA   |

| V <sub>CM</sub> | Common-Mode Input Range                |                            | 1                         | V-                     |                           | (V+) - 1.5 | V    |

| CMRR            | Common-Mode Rejection Ratio            | V- to (V+ - 1.5V)          | MSOP Package              |                        | 1.2                       | 3          | mV/V |

|                 |                                        |                            |                           |                        |                           | 3.5        | mV/V |

|                 |                                        |                            | TDFN Package              |                        | 1.2                       | 4.5        | mV/V |

|                 |                                        |                            |                           |                        |                           | 5          | mV/V |

# Analog Specifications (V+ = +5.0V) V- = GND = OV unless otherwise specified, $T_A = +25 \,^{\circ}C$ . Boldface limits apply across the operating temperature range, -40 $^{\circ}C$ to +125 $^{\circ}C$ . (Continued)

| SYMBOL            | PARAMETER                                  | TEST CO                                                   | ONDITIONS         | MIN<br>( <u>Note 11</u> ) | TYP<br>(Note 10) | MAX<br>( <u>Note 11</u> ) | UNIT |

|-------------------|--------------------------------------------|-----------------------------------------------------------|-------------------|---------------------------|------------------|---------------------------|------|

| PSRR              | Power Supply Rejection Ratio               | V+ = 2V to 11V                                            | MSOP Package      |                           | 0.25             | 1.1                       | mV/V |

|                   |                                            |                                                           |                   |                           |                  | 1.2                       | mV/V |

|                   |                                            |                                                           | TDFN Package      |                           | 0.25             | 1.5                       | mV/V |

|                   |                                            |                                                           |                   |                           |                  | 1.6                       | mV/V |

| V <sub>HYST</sub> | Hysteresis Input Voltage                   |                                                           | 1                 | REF - 50mV                |                  | REF                       | ٧    |

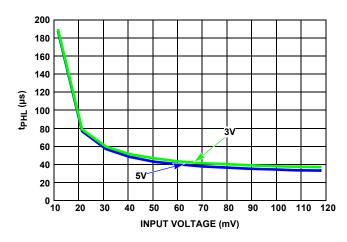

| t <sub>PHL</sub>  | Propagation Delay - HIGH to LOW Transition | C <sub>L</sub> = 100pF                                    | Overdrive = 10mV  |                           | 100              |                           | μs   |

|                   |                                            |                                                           | Overdrive = 100mV |                           | 50               |                           | μs   |

| t <sub>PLH</sub>  | Propagation Delay - LOW to HIGH Transition | C <sub>L</sub> = 100pF Overdrive = 10mV Overdrive = 100mV | Overdrive = 10mV  |                           | 200              |                           | μs   |

|                   |                                            |                                                           |                   | 100                       |                  | μs                        |      |

| V <sub>OH</sub>   | Output High Voltage                        | I <sub>O</sub> = -10mA                                    |                   | (V+) - 0.4                |                  |                           | ٧    |

| V <sub>OL</sub>   | Output Low Voltage                         | I <sub>O</sub> = 3mA                                      |                   |                           |                  | GND + 0.6                 | ٧    |

| REFERENCI         | Ē                                          | 1                                                         |                   |                           |                  | 1                         |      |

| V <sub>REF</sub>  | Reference Voltage                          | No Load                                                   |                   | 1.176                     |                  | 1.188                     | ٧    |

| $\Delta V_{REF}$  | Output Load Regulation                     | 0 ≤ I <sub>SOURCE</sub> ≤ 2mA                             |                   |                           | -0.5             | -2.0                      | m۷   |

|                   |                                            |                                                           |                   |                           |                  | -2.5                      | m۷   |

|                   |                                            | 0 ≤ I <sub>SINK</sub> ≤ 10μA                              |                   |                           | 0.1              | 2.0                       | m۷   |

|                   |                                            |                                                           |                   |                           |                  | 2.5                       | m۷   |

# Analog Specifications (V+ = +3.0V) $V_{-} = GND = 0V$ unless otherwise specified, $T_A = +25$ °C. Boldface limits apply across the operating temperature range, -40°C to +125°C.

| SYMBOL          | PARAMETER                              | TEST CONDITIONS                                |              | MIN<br>( <u>Note 11</u> ) | TYP<br>(Note 10) | MAX<br>(Note 11) | UNIT |

|-----------------|----------------------------------------|------------------------------------------------|--------------|---------------------------|------------------|------------------|------|

| V+ = 3.0V, \    | /- = GND = OV                          |                                                |              | •                         | 1                |                  |      |

| Icc             | Supply Current                         | IN+ = IN- +80mV, H                             | YST = REF    |                           | 0.40             | 0.7              | μΑ   |

|                 |                                        |                                                |              |                           |                  | 5                | μΑ   |

| COMPARAT        | OR                                     | ,                                              |              |                           | 1                |                  |      |

| Vos             | Input offset Voltage                   | V <sub>CM</sub> = 1.5V                         | MSOP Package |                           | ±2.3             | ±3.4             | mV   |

|                 |                                        |                                                |              |                           |                  | ±3.5             | mV   |

|                 |                                        |                                                | TDFN Package |                           | ±2.3             | ±4.2             | mV   |

|                 |                                        |                                                |              |                           |                  | ±4.3             | m۷   |

| I <sub>IN</sub> | Input Leakage Current (IN+, IN-, HYST) | ut (IN+, IN-, HYST) $V_{IN+} = V_{IN-} = 1.5V$ |              |                           | 0.1              | 1.1              | nA   |

|                 |                                        |                                                |              |                           |                  | 3                | nA   |

| V <sub>CM</sub> | Common-Mode Input Range                |                                                |              | V-                        |                  | (V+) - 1.5       | ٧    |

| CMRR            | Common-Mode Rejection Ratio            | V- to (V+ - 1.5V)                              | MSOP Package |                           | 1.2              | 5                | mV/V |

|                 |                                        |                                                |              |                           |                  | 5.5              | mV/V |

|                 |                                        |                                                | TDFN Package |                           | 1.2              | 7.5              | mV/V |

|                 |                                        |                                                |              |                           |                  | 8                | mV/V |

# Analog Specifications (V+ = +3.0V) $V_{-} = GND = 0V$ unless otherwise specified, $T_A = +25^{\circ}C$ . Boldface limits apply across the operating temperature range, -40°C to +125°C. (Continued)

| SYMBOL            | PARAMETER                                  | TEST C                        | ONDITIONS         | MIN<br>( <u>Note 11</u> ) | TYP<br>(Note 10) | MAX<br>( <u>Note 11</u> ) | UNIT |

|-------------------|--------------------------------------------|-------------------------------|-------------------|---------------------------|------------------|---------------------------|------|

| PSRR              | Power Supply Rejection Ratio               | V+ = 2V to 11V                | MSOP Package      |                           | 0.25             | 1.1                       | mV/V |

|                   |                                            |                               |                   |                           |                  | 1.2                       | mV/V |

|                   |                                            |                               | TDFN Package      |                           | 0.25             | 1.5                       | mV/V |

|                   |                                            |                               |                   |                           |                  | 1.6                       | mV/V |

| V <sub>HYST</sub> | Hysteresis Input Voltage                   |                               |                   | REF - 50mV                |                  | REF                       | ٧    |

| t <sub>PHL</sub>  | Propagation Delay - HIGH to LOW Transition | C <sub>L</sub> = 100pF        | Overdrive = 10mV  |                           | 100              |                           | μs   |

|                   |                                            |                               | Overdrive = 100mV |                           | 50               |                           | μs   |

| t <sub>PLH</sub>  | Propagation Delay - LOW to HIGH Transition | C <sub>L</sub> = 100pF        | Overdrive = 10mV  |                           | 200              |                           | μs   |

|                   | Overdrive = 100n                           | Overdrive = 100mV             |                   | 100                       |                  | μs                        |      |

| V <sub>OH</sub>   | Output High Voltage                        | I <sub>O</sub> = -6mA         |                   | (V+) - 0.4                |                  |                           | ٧    |

| V <sub>OL</sub>   | Output Low Voltage                         | I <sub>O</sub> = 1.8mA        |                   |                           |                  | GND + 0.6                 | ٧    |

| REFERENC          | Ε                                          |                               |                   | "                         | I                | II.                       |      |

| V <sub>REF</sub>  | Reference Voltage                          | No Load                       |                   | 1.176                     |                  | 1.188                     | ٧    |

| ΔV <sub>REF</sub> | Output Load Regulation                     | 0 ≤ I <sub>SOURCE</sub> ≤ 2mA |                   |                           | -0.5             | -2.0                      | m۷   |

|                   |                                            |                               |                   |                           |                  | -2.5                      | m۷   |

|                   |                                            | 0 ≤ I <sub>SINK</sub> ≤ 10μA  |                   |                           | 0.1              | 2.0                       | mV   |

|                   |                                            |                               |                   |                           |                  | -2.5                      | m۷   |

#### NOTES:

- 10. Across the specified temperature range. Temperature coefficient is measured by the box method whereby the change in V<sub>OUT</sub> is divided by the temperature range; in this case, -40°C to +125°C = +165°C.

- 11. Parts are 100% tested at +25°C and +85°C. The -40°C and +125°C temperature limits are established by characterization and are not production tested.

## **Typical Performance Curves**

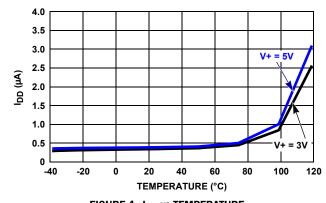

FIGURE 4.  $I_{\mbox{\scriptsize DD}}$  vs TEMPERATURE

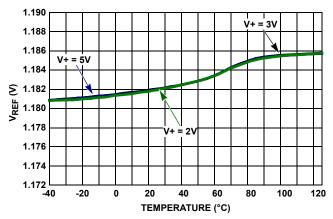

FIGURE 6. V<sub>REF</sub> vs TEMPERATURE

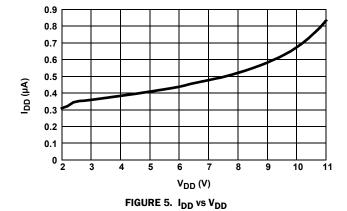

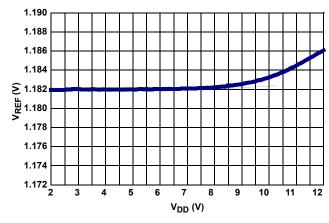

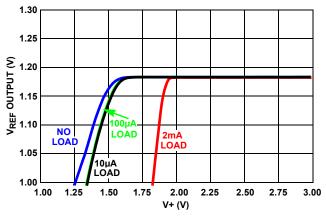

FIGURE 7. V<sub>REF</sub> vs SUPPLY VOLTAGE

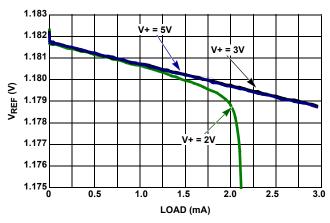

FIGURE 8. V<sub>REF</sub> vs LOAD (SOURCE)

FIGURE 9. V<sub>REF</sub> vs LOAD (SINK)

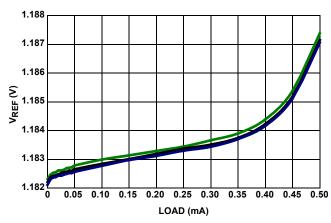

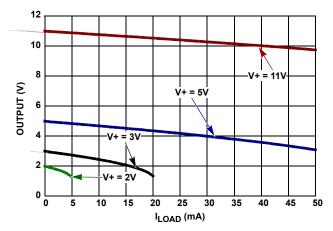

FIGURE 10. VREF DROPOUT vs VREF OUTPUT vs LOAD

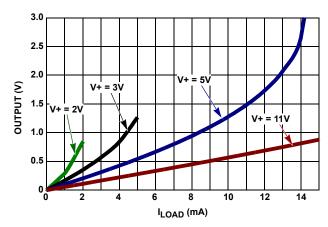

FIGURE 11. COMPARATOR OUTPUT LOW VOLTAGE vs LOAD

FIGURE 12. COMPARATOR OUTPUT HIGH VOLTAGE vs LOAD

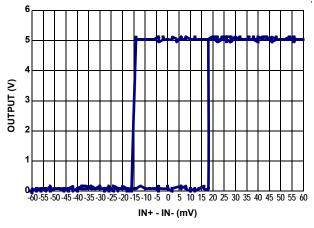

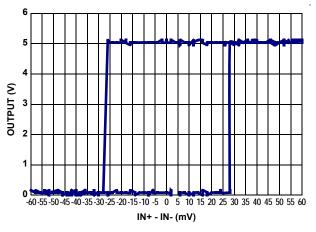

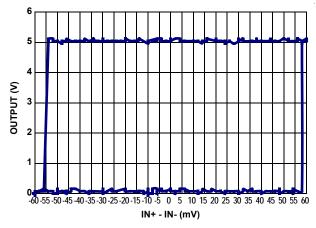

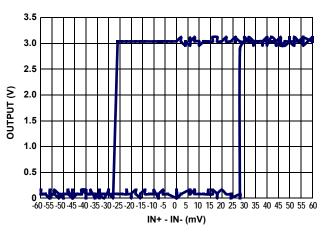

FIGURE 14. HYSTERESIS - 12.5mV (V+ = 5V)

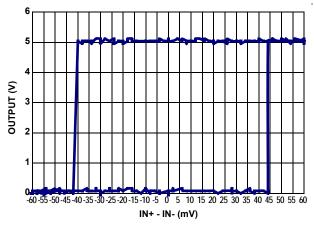

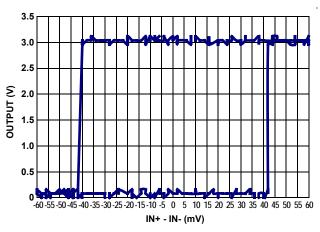

FIGURE 16. HYSTERESIS - 37.5mV (V+ = 5V)

FIGURE 13. HYSTERESIS - 0mV (V+ = 5V)

FIGURE 15. HYSTERESIS - 25mV (V+ = 5V)

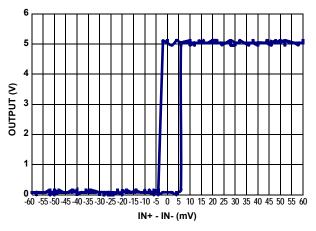

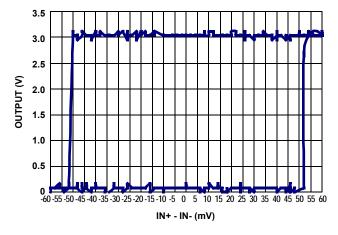

FIGURE 17. HYSTERESIS - 50mV (V+ = 5V)

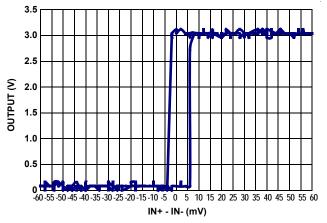

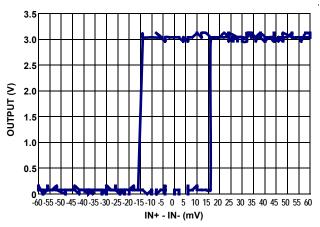

FIGURE 18. HYSTERESIS - 0mV (V+ = 3V)

FIGURE 19. HYSTERESIS - 12.5mV (V+ = 3V)

FIGURE 20. HYSTERESIS - 25mV (V+ = 3V)

FIGURE 21. HYSTERESIS - 37.5mV (V+ = 3V)

FIGURE 22. HYSTERESIS - 50mV (V+ = 3V)

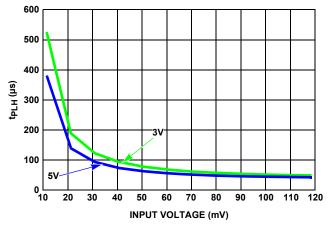

FIGURE 23. OUTPUT RESPONSE TIME vs INPUT OVERDRIVE ( $t_{PHL}$ )

FIGURE 24. OUTPUT RESPONSE TIME vs INPUT OVERDRIVE ( $t_{PLH}$ )

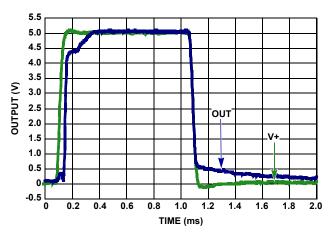

FIGURE 25. POWER-UP/DOWN OUTPUT RESPONSE (V+ = 5V, IN+ = V+, IN- =  $V_{REF}$ )

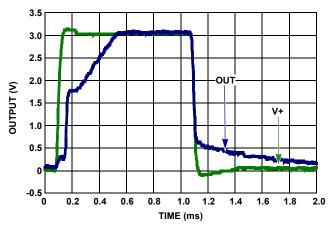

FIGURE 26. POWER-UP/DOWN OUTPUT RESPONSE (V+ = 3V, IN+ = V+, IN- =  $V_{REF}$ )

### **Functional Description**

### **Device Power**

The ISL21440 device has a single positive supply pin, V+, and two other supply pins, V- and GND. Normally, for single supply applications the V- pin is tied to system ground as well as the GND pin. The separate ground pin allows the comparator to be powered by split supplies from  $\pm 1.0 \text{V}$  to  $\pm 5.5 \text{V}$ . Note that the minimum supply voltage will be 0.8V above the comparator maximum input level for accurate operation.

### **Comparator Section**

The comparator inputs can swing from the negative supply (GND pin) to within 0.8V of the positive supply (V+). Alternatively, with the comparator input set at the 1.182V reference level, the minimum input voltage for accurate operation is 2.0V. If the inputs are expected to see voltage levels above V+ or below ground, they should be clamped with low leakage Schottky diodes.

The CMOS output swings essentially from the GND potential to V+ potential, depending on load current. If loads in excess of 1mA are expected, then a  $0.1\mu F$  decoupling capacitor at the V+ pin should be added.

### **Voltage Reference Section**

The voltage reference is a micropower FGA reference and is set to 1.182V  $\pm 0.5\%$  at the factory. The reference output can source up to 2mA but the sink capability is very limited at only 10µA, maximum. Small value capacitors, up to 10nF, can be used on the reference output to lower noise if desired.

### **Applications Information**

### **Handling and Board Mounting**

FGA references provide excellent initial accuracy and low temperature drift at the expense of very little power drain. There are some precautions to take to insure this accuracy is not compromised. Excessive heat during solder reflow can cause excessive initial accuracy drift, so the recommended +260 °C maximum temperature profile should not be exceeded. Expect up to 1mV drift from the solder reflow process.

FGA references are susceptible to excessive X-radiation like that used in PC board manufacturing. Initial accuracy can change 10mV or more under extreme radiation. If an assembled board needs to be X-rayed, care should be taken to shield the FGA reference device.

#### **Hysteresis**

The Hysteresis function allows for changing the value of the reference switchover point depending on the previous state of the comparator. This works to remove the effects of noise or glitches in the voltage detection input and provide more reliable output transitions.

Hysteresis is added to the ISL21440 by connecting one resistor between the REF and HYST pins (R<sub>REF</sub>), and another resistor(R<sub>HYST</sub>) between the HYST pin and ground. The hysteresis voltage (V<sub>H</sub>) is designed to be twice the voltage difference

between the HYST pin and REF pin ( $V_H = 2 * (V_{REF} - V_{HYST})$ ). Since the reference voltage is 1.182V ( $V_{REF}$ ), Equations 1 and 2 for these two resistors are shown as follows:

$$R_{REF} = V_{H}/(2*I_{REF}) = (V_{REF} - V_{HYST})/I_{REF}$$

(EQ. 1)

$$R_{HYST} = (1.182 - V_{H}/2)/I_{REF} = V_{HYST}/I_{REF}$$

(EQ. 2)

$I_{REF}$  is chosen to be less than the maximum output of the reference, usually  $5\mu A$  is a safe value but for lowest power,  $0.1\mu A$  can be used.

If the hysteresis is not used, the HYST pin should be tied to the REF pin.

### **Board Assembly Considerations**

FGA references provide high accuracy and low temperature drift but some PC board assembly precautions are necessary. Normal output voltage shifts of  $100\mu V$  to 1mV can be expected with Pb-free reflow profiles or wave solder on multilayer FR4 PC boards. Precautions should be taken to avoid excessive heat or extended exposure to high reflow or wave solder temperatures, which may reduce device initial accuracy.

Post-assembly X-ray inspection may also lead to permanent changes in device output voltage and should be minimized or avoided. If X-ray inspection is required, it is advisable to monitor the reference output voltage to verify excessive shift has not occurred. If large amounts of shift are observed, it is best to add an X-ray shield consisting of thin zinc (300µm) sheeting to allow clear imaging, yet block x-ray energy that affects the FGA reference.

### **Special Applications Considerations**

In addition to post-assembly examination, there are also other X-ray sources that may affect the FGA reference long term accuracy. Airport screening machines contain X-rays and will have a cumulative effect on the voltage reference output accuracy. Carry-on luggage screening uses low level X-rays and is not a major source of output voltage shift, although if a product is expected to pass through that type of screening over 100 times it may need to consider shielding with copper or aluminum. Checked luggage X-rays are higher intensity and can cause output voltage shift in much fewer passes, so devices expected to go through those machines should definitely consider shielding. Note that just two layers of 1/2 ounce copper planes will reduce the received dose by over 90%. The lead frame for the device, which is on the bottom, also provides similar shielding.

If a device is expected to pass through luggage X-ray machines numerous times, it is advised to mount a 2-layer (minimum) PC board over the top of the package, which, along with a ground plane underneath, will effectively shield it from 50 to 100 passes through the machine. Since these machines vary in X-ray dose delivered, it is difficult to produce an accurate maximum pass recommendation.

### **Typical Applications**

### **Low Battery Detector**

Figure 27 shows a typical implementation for the ISL21440, a low battery detector. The values for R<sub>REF</sub> and R<sub>HYST</sub> provide 20mV of hysteresis and 0.5μA I<sub>REF</sub>. The input trip point for V<sub>DETECT</sub> is the same as the reference voltage, 1.182V, and a resistor divider at the input sets the Lo<sub>BAT</sub> trip point at 2.7V. The total current draw for the circuit is going to be 1.1μA for V<sub>DD</sub> and 0.6μA for V<sub>BAT</sub>.

FIGURE 27. LOW BATTERY DETECTOR WITH HYSTERESIS

### **Window Comparator**

The ISL21440 can be combined with a micropower comparator to produce a window comparator circuit. The circuit in Figure 28 uses a 3-resistor divider to produce high and low trip points and the ISL28197 (800nA supply current) comparator is added to give the second output. The two outputs can be used separately for overvoltage or undervoltage indication, or a gate can be added as shown to report either in-window or out-of window condition.

The resistors are shown as **Equations 3**, **4**, and **5** as follows.

Set:

$$R_3 = 1M(1\%)$$

(EQ. 3)

$$R_2 = R_3[V_H/V_L - 1]$$

(EQ. 4)

$$R_1 = R_3([V_H/V_{RFF}-1]-R_2)$$

(EQ. 5)

Example: For  $V_H = 3.8V$ ,  $V_L = 2.7V$  (3.3V  $\pm$  0.5V)

$R_2 = 402k, R_1 = 1.82M$  (can be 1%)

The resulting circuit draws about  $3\mu A$  and works down to  $V_{DD}$  = 2.2V.

FIGURE 28. WINDOW COMPARATOR CIRCUIT

# **Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mar 24, 2017 | FN6532.4 | Updated V <sub>OL</sub> maximum specification for both 3V and 5V supply conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Mar 3, 2016  | FN6532.3 | On pages 3 and page 4 in Electrical Spec table (Analog Specifications): Changed ICC Supply Current Max Limit across Temperature from: 0.85µA, to: 5µA. Updated typical performance curves Figures 3, 4, 9, 22, 23. Updated POD M8.118 to most current version with revision of POD as follows: Corrected lead width dimension in side view 1 from "0.25 - 0.036" to "0.25 - 0.36" Updated POD L8.3x3G to most current version with revision of POD as follows: Tiebar Note updated From: Tiebar shown (if present) is a non-functional feature. To: Tiebar shown (if present) is a non-functional feature and may be located on any of the 4 sides (or ends). Updated Product to About Intersil |

| Jan 24, 2011 | FN6532.2 | On page 2: Updated Tape & Reel note in "Ordering Information" to add new standard "Add "-T*" suffix for tape and reel." The "*" covers all possible tape and reel options  On page 4: Separated "Analog Specifications" tables into 2 tables. Put specs from "V+ = 3.0V, V- = GND = 0V" to end of table into separate table and added following common conditions: "V+= +3.0V. V- = GND = 0V unless otherwise specified, T <sub>A</sub> = +25°C. Boldface limits apply over the operating temperature range, -40°C to +125°C."                                                                                                                                                                  |

|              |          | On page 4: Changed conditions for "V <sub>OH</sub> " from Io = -7mA to Io = -6mA  Changed conditions for "V <sub>OL</sub> " from Io = 3mA to Io = 1.8mA In "Window Comparator" on page 11, changed "with a micropower to" to: "with a micropower comparator to" Page 14, replaced POD M8.118 with newest revision. Updated to new intersil format by adding land pattern and moving dimensions from table onto drawing                                                                                                                                                                                                                                                                          |

| Mar 2, 2010  | FN6532.1 | Updated datasheet with the TDFN spec.  Spec added on pages 5-6 are: VOS, IIN, CMRR and PSRR. Each spec has an added row for the TDFN package and the original limit for the MSOP package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Dec 7, 2009  | FN6532.0 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing, and high-end consumer markets.

For the most updated datasheet, application notes, related documentation, and related parts, see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

For a listing of definitions and abbreviations of common terms used in our documents, visit www.intersil.com/glossary.

You can report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

© Copyright Intersil Americas LLC 2009-2017. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

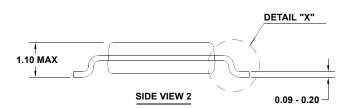

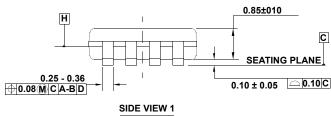

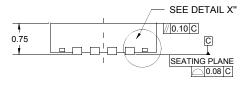

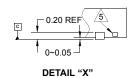

## **Package Outline Drawing**

M8.118

8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

Rev 4, 7/11

For the most recent package outline drawing, see M8.118.

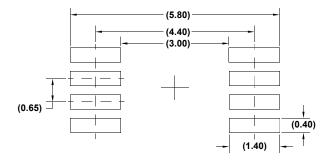

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters.

- Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSEY14.5m-1994.

- Plastic or metal protrusions of 0.15mm max per side are not included.

- Plastic interlead protrusions of 0.15mm max per side are not included.

- 5. Dimensions are measured at Datum Plane "H".

- 6. Dimensions in ( ) are for reference only.

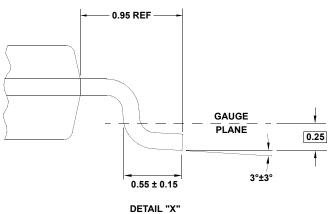

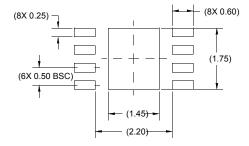

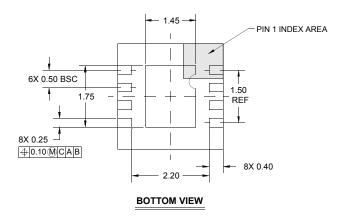

## **Package Outline Drawing**

L8.3x3G

8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE (TDFN) Rev 1, 5/15

TYPICAL RECOMMENDED LAND PATTERN

For the most recent package outline drawing, see <u>L8.3x3G</u>.

SIDE VIEW

\_\_\_

#### NOTES:

- Controlling dimensions are in mm.

Dimensions in ( ) for reference only.

- 2. Unless otherwise specified, tolerance: Decimal  $\pm 0.05$  Angular  $\pm 2^{\circ}$

- 3. Dimensioning and tolerancing conform to JEDEC STD MO220-D.

- 4. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 5. Tiebar shown (if present) is a non-functional feature and may be located on any of the 4 sides (or ends).