# **Active PFC Controller with Critical Conduction Mode**

# **General Description**

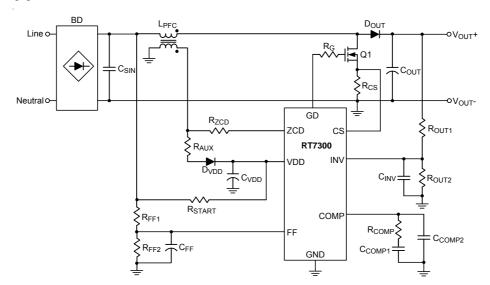

The RT7300 is an active Power Factor Correction (PFC) controller with critical conduction mode (CRM) operation that is designed to meet line current harmonic regulations for the applications of AC/DC adapters, electronic ballasts and medium off-line power converters (<300W). The CRM and Feed-Forward schemes provide near unity power factor across a wide range of input voltages and output powers.

The totem-pole gate driver with 600mA sourcing current and 800mA sinking current provides powerful driving capability for power MOSFET to improve conversion efficiency. The RT7300 features an extra low start-up current ( $\leq$ 20µA) and supports a disable function to reduce power consumption in standby mode, which makes it easy to comply with energy saving regulations such as Blue Angel, Energy Star and Energy 2000.

This controller integrates comprehensive safety protection functions for robust designs including input under voltage lockout, output over voltage protection, under voltage protection and cycle-by-cycle current limit.

The RT7300 is a cost-effective solution for PFC power converter with minimum external components. It is available in the SOP-8 package.

### **Features**

- Critical Conduction Mode (CRM) Operation

- Constant On-Time Control (Voltage Mode)

- Near Unity Power Factor

- Ultra Low Start-up Current (<20μA)</li>

- Input Voltage Feed-Forward Compensation

- Wide Supply Voltage Range from 12V to 25V

- Totem Pole Gate Driver with 600mA/-800mA

- Maximum Frequency Clamping (120kHz)

- DCM THD Optimization

- Fast Dynamic Response

- Light Load Burst Mode Operation

- Brown-in/Brown-out Detection

- Disable Function

- Maximum/Minimum On-Time Limit

- Cycle-by-Cycle Current Limit

- Output Over Voltage Protection (OVP)

- Output Under Voltage Protection (UVP)

- Under Voltage Lockout (UVLO)

- RoHS Compliant and Halogen Free

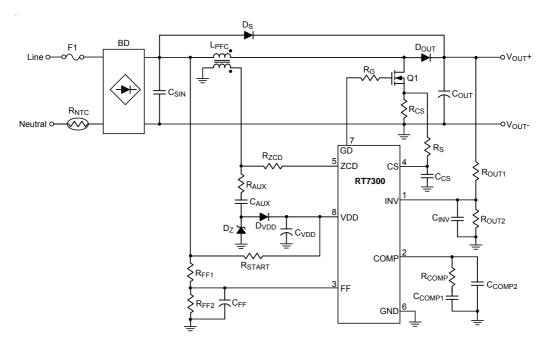

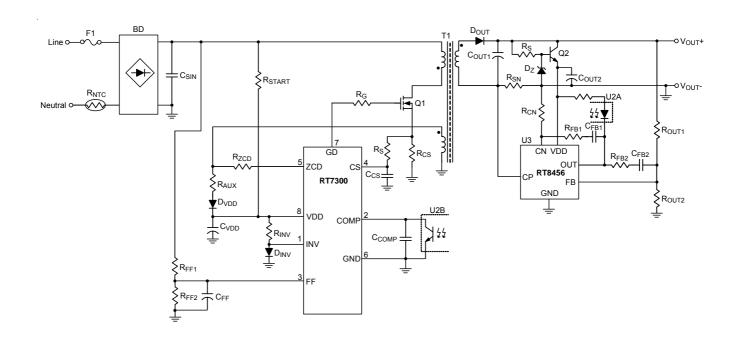

# **Simplified Application Circuit**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Applications**

- Electrical Lamp Ballast

- LED Lighting

- AC/DC Adapter/Charger for Desktop PC, NB, TV, Monitor, Etc.

- Entry-Level Server, Web Server

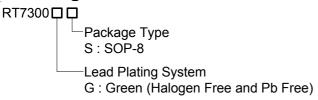

# **Ordering Information**

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

RT7300GS: Product Number

YMDNN: Date Code

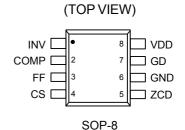

## **Pin Configurations**

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                           |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INV      | Inverting Input of the Internal Error Amplifier. Connect a resistive divider from output voltage to this pin for voltage feedback. It also used for OVP and UVP detections.            |

| 2       | COMP     | Output of the Internal Error Amplifier. Connect a compensation network between this pin and GND for dynamic load performance.                                                          |

| 3       | FF       | Feed-Forward Input for Line Voltage. This pin senses the line input voltage via a resistive divider. Connect a suitable capacitor to filter out the line voltage ripple & noise.       |

| 4       | cs       | Current Sense Input. The current sense resistor between this pin and GND is used for current limit setting.                                                                            |

| 5       | ZCD      | Zero Current Detection Input. Input from secondary winding of PFC choke for detecting demagnetization timing of PFC choke. This pin also can be used to enable/disable the controller. |

| 6       | GND      | Ground of the Controller.                                                                                                                                                              |

| 7       | GD       | Gate Driver Output for External Power MOSFET.                                                                                                                                          |

| 8       | VDD      | Supply Voltage Input. The controller will be enabled when VDD exceeds Von_th (16V typ.) and disabled when VDD decreases lower than Voff_th (9V typ.).                                  |

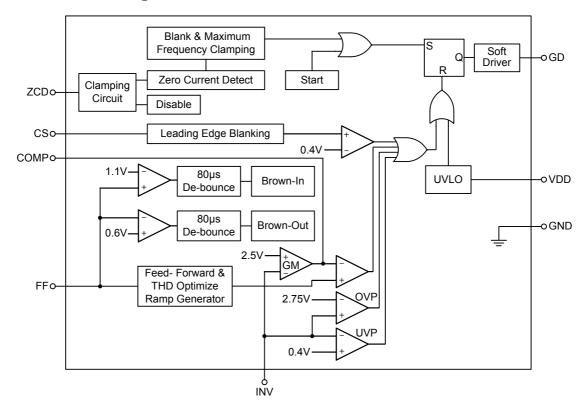

# **Function Block Diagram**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

## **Operation**

### **Critical Conduction Mode (CRM)**

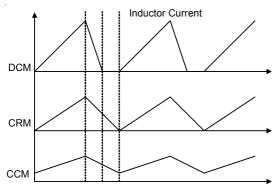

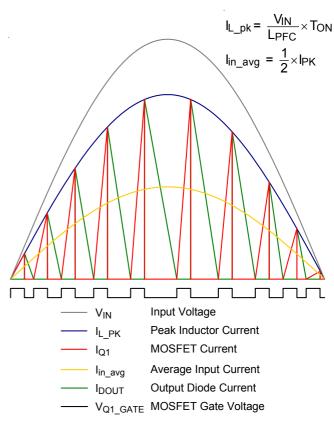

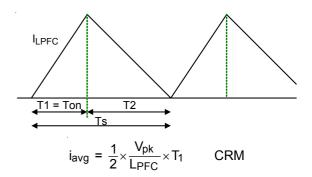

The Critical Conduction Mode is also called Transition Mode or Boundary Mode. Figure 1 shows the CRM operating at the boundary between Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM).

In CRM, the power switch turns on immediately when the inductor current decreases to zero. The CRM is the preferred control method for medium power (<300W) applications due to the features of zero current switching and lower peak current than that in DCM.

Figure 1. Inductor Current of DCM, CRM and CCM

### **Constant On-Time Voltage Mode Control**

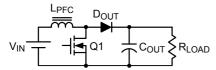

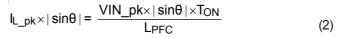

Figure 2 shows a typical Boost converter. When the MOSFET turns on with a fixed on-time (T<sub>ON</sub>), the inductor current can be calculated by the following equation (1).

Figure 2. Typical Boost Converter

$$I_{L\_PK} = \frac{V_{IN}}{L_{PFC}} \times T_{ON}$$

(1)

If the input voltage is a sinusoidal waveform and rectified by a bridge rectifier, the inductor current can be expressed with equation (2). When the converter operates in CRM with constant on-time voltage mode control, the envelope of inductor peak current will follow the input voltage waveform with in-phase. The average inductor current will be half of the peak current shown as Figure 3. Therefore, the near unity power factor is easy to be achieved by this control scheme.

Figure 3. Inductor Current of CRM with Constant On-Time Voltage Mode Control

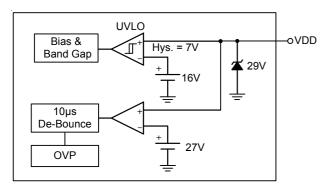

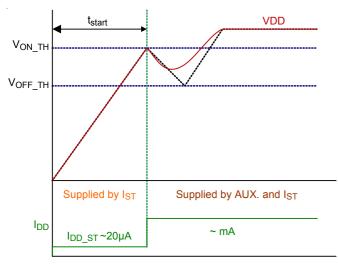

#### **Under Voltage Lockout**

The controller will be enabled when VDD exceeds Von\_th (16V typ.) and disabled when VDD decreases lower than Voff\_th (9V typ.).

The maximum VDD voltage is set at 27V typically for over voltage protection shown as Figure 4. An internal 29V zener diode is also used to avoid over voltage stress for the internal circuits.

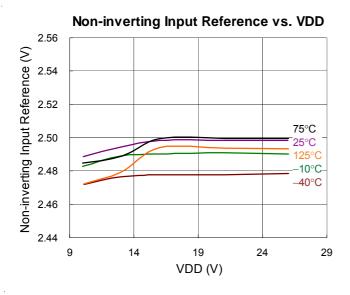

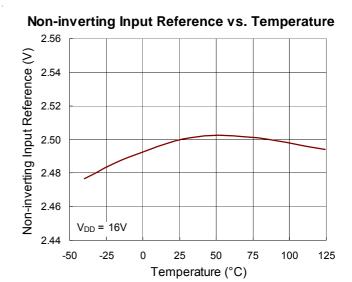

When the VDD is available, the precise reference is generated for internal circuitries such as Error Amplifier, Current Sense, OVP, UVP, Brown-in and Brown-out. The internal reference equips with excellent temperature coefficient performance so that the RT7300 can be operated in varied environments.

4

Figure 4. VDD and UVLO

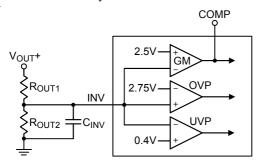

## **Feedback Voltage Detection**

Figure 5 shows the feedback voltage detection circuit. The INV pin is the inverting input of the Error Amplifier with 2.5V reference voltage. Over voltage and under voltage protections are provided with threshold voltage 2.75V and 0.4V respectively. If the INV voltage is over 2.75V or under 0.4V, the gate driver will be disabled to prevent output over voltage condition or feedback open condition. Although the INV is an input pin with high impedance, it is suggested that the bias current of the potential divider should be over  $30\mu A$  for noise immunity.

Figure 5. Feedback Voltage Detection

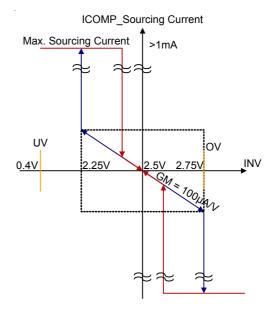

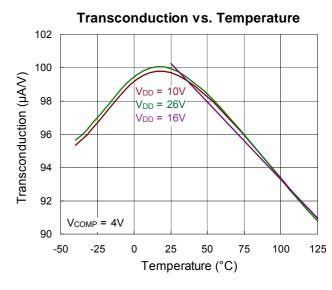

### **Transconductance Error Amplifier**

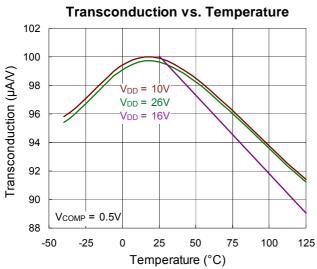

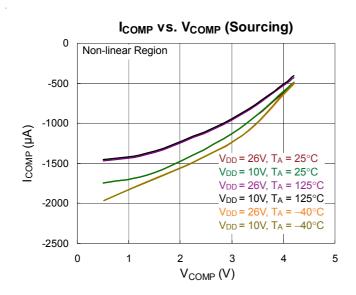

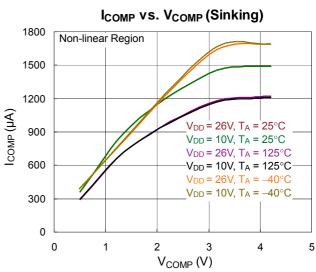

The RT7300 implements transconductance error amplifier with non-linear GM design to regulate the Boost output voltage and provide fast dynamic response. The transconductance value is 100µA/V in normal operation. When the INV voltage increases over 2.75V or decreases under 2.25V, the output of error amplifier will source or sink 1mA maximum current at COMP pin respectively shown as Figure 6. Thus, the non-linear GM design can provide fast response for the dynamic load of PFC converters even though the bandwidth of control loop is lower than line frequency.

Figure 6. Non-linear GM

### **Feed-Forward Compensation**

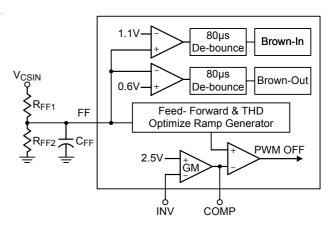

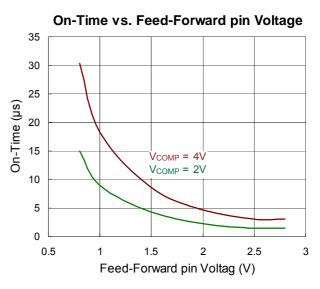

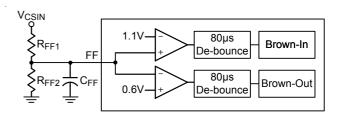

The FF pin is an input pin with high impedance to detect the line input voltage shown as Figure 7. A proper voltage divider should be applied to sense the line voltage after bridge diode rectifier. Since the FF voltage is proportional to the line input voltage, it provides a feed-forward signal to compensate the loop bandwidth for high line and low line input conditions. The FF pin is also used for the detection of Brown-in and Brown-out functions to protect converter from over stress at low input voltage situation.

Figure 7. FF Detection Circuit

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

The constant on-time, T<sub>ON</sub>, can be derived from the following equations.

$$P_{i} = \frac{1}{4} \times V_{pk} \times I_{L\_pk} \qquad I_{L\_pk} = \frac{V_{pk}}{L_{PFC}} \times T_{ON}$$

$$P_{i} = \frac{1}{4} \times V_{pk} \times \frac{V_{pk}}{L_{PFC}} \times T_{ON} = \frac{1}{4} \times \frac{V_{pk}^{2}}{L_{PFC}} \times T_{ON}$$

$$\Rightarrow T_{ON} = \frac{4 \times P_{i} \times L_{PFC}}{V_{pk}^{2}}$$

(3)

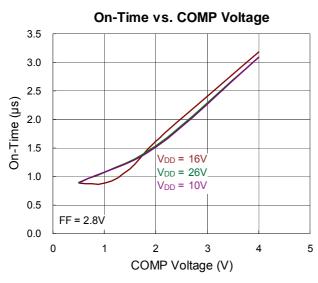

In RT7300, the Ton is implemented by a constant current charging a capacitor till V<sub>Comp</sub> threshold voltage is reached. Therefore, the T<sub>ON</sub> is a function of Vcomp.

$$T_{ON} = \frac{C_{ramp} \times V_{Comp}}{I_{ramp}}$$

(4)

Then, the V<sub>Comp</sub> can be derived from equation (3) and (4).

$$\frac{4 \times P_{i} \times L_{PFC}}{V_{pk}^{2}} = \frac{C_{ramp} \times V_{Comp}}{I_{ramp}}$$

$$V_{Comp} = \frac{4 \times P_{i} \times L_{PFC}}{V_{pk}^{2}} \times \frac{I_{ramp}}{C_{ramp}}$$

(5)

According to equation (5), the V<sub>Comp</sub> is reversely proportional to the squared input voltage so that the V<sub>Comp</sub> has a large variation for the change of line voltage between high and low input voltages. This variation will impact T<sub>ON</sub>, Burst mode entry level and loop bandwidth.

In order to compensate the variation, the Iramp is designed to be proportional to the squared input voltage shown as equation (6).

$$I_{ramp}(V_{pk}) = k \times V_{pk}^2 \times gm_{ramp}$$

(6)

$$V_{Comp}(FF) = \frac{2 \times P_i \times L_{PFC} \times gm_{ramp}}{C_{ramp}}$$

(7)

When k = 0.5, the Vcomp is compensated to be proportional to the power only. So, the Ton will be stable to support good power factor for high and low line voltage conditions.

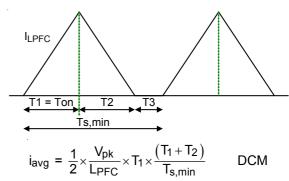

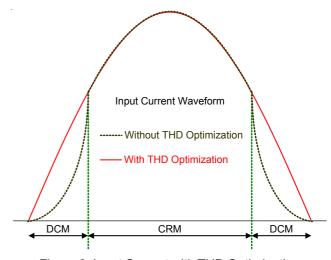

#### **THD Optimization**

www.richtek.com

When the controller operates in a very low input voltage level, the switching frequency will be clamped at a maximum frequency 120kHz to reduce EMI. In this condition, the inductor current will be operated in DCM, the input average current will be distorted due to the blank duration T3 shown as Figure 8.

Figure 8. Inductor Current in CRM and DCM

In order to compensate the distortion of DCM operation, the average current in DCM must be equal to the average current in CRM. It is implemented by increasing the ontime (I<sub>ramp</sub>) in DCM to achieve the optimized THD for input current.

$$T'_1 = T_1 \times \frac{T_{S,min}}{(T_1 + T_2)} = T_1 \times \frac{1}{D'}$$

(8)

$$I'_{ramp} = I_{ramp} \times D' \tag{9}$$

Figure 9. Input Current with THD Optimization

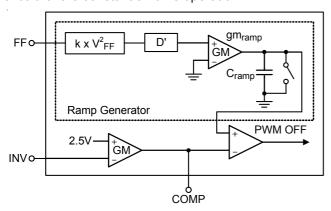

### **Ramp Generator**

The RT7300 provides constant on-time voltage mode control to achieve near unity power factor for the CRM boost converters. Figure 10 shows the Ramp Generator with Feed-Forward compensation and THD optimization circuit for the constant on-time operation.

Figure 10. Ramp Generator

The capacitance Cramp is 6.5pF (typ.).

The charging current of ramp generator is modulated following the squared FF voltage with line voltage compensation and the THD optimization scheme is implemented to compensate the harmonic distortion when the converter is operated in DCM.

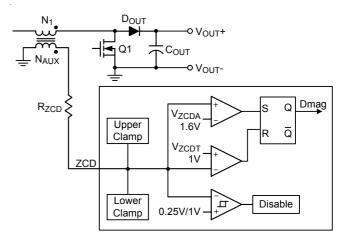

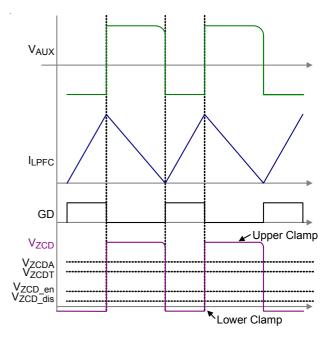

#### **ZCD** and Enable Function

In CRM operation, when the power switch turns on, the inductor current increases linearly to the peak value. When the power switch turns off, the inductor current decreases linearly to zero. The zero current can be detected by the ZCD pin with the auxiliary winding of Boost inductor.

Figure 11 and Figure 12 show the ZCD block diagram and related waveforms. The ZCD block diagram provides zero current detection, voltage clamp and shutdown control functions. When the inductor current decreases to zero, the auxiliary winding voltage will turn from high to low. Once the ZCD voltage decreases to the  $V_{ZCDT}$  threshold, the controller will generate a signal for gate driver. The hysteresis voltage between the threshold  $V_{ZCDA}$  and  $V_{ZCDT}$  is designed to avoid mis-triggering. In order to prevent over voltage stress, the ZCD pin voltage is clamped at  $V_{ZCDH}$  if the input voltage is too high from the auxiliary winding and the ZCD pin voltage is clamped at  $V_{ZCDL}$  if the input voltage is lower than zero.

Figure 11. ZCD Block Diagram

The RT7300 provides shutdown function to save power consumption in standby mode. When the ZCD pin is pulled lower than 250mV, the gate driver will be turned off and operate in standby mode with low quiescent current less than  $600\mu A$ . Once the ZCD pin is released, the controller will be activated.

The RT7300 also provides ZCD time-out detection function. If the controller runs at maximum frequency and there is no ZCD signal being detected after  $4\mu s$  delay time, the PWM will be turned on for ZCD time-out detection.

Figure 12. ZCD Related Waveforms

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Absolute Maximum Ratings (Note 1)

| • Supply Voltage, VDD                                                       | -0.3 to 30V    |

|-----------------------------------------------------------------------------|----------------|

| • Gate Driver Output, GD                                                    | -0.3V to 20V   |

| • Other Pins                                                                | -0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| SOP-8                                                                       | 0.625W         |

| Package Thermal Resistance (Note 2)                                         |                |

| SOP-8, $\theta_{JA}$                                                        | - 160°C/W      |

| • Junction Temperature                                                      |                |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C        |

| Storage Temperature Range                                                   | -65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Model)                                                      | · 2kV          |

| MM (Machine Model)                                                          | - 200V         |

|                                                                             |                |

| Recommended Operating Conditions (Note 4)                                   |                |

| • Supply Voltage, VDD                                                       | 12V to 25V     |

• Junction Temperature Range ------ -40°C to 125°C

# **Electrical Characteristics**

( $V_{DD}$  = 15V,  $T_A$  = 25°C, unless otherwise specification)

| Parameter                                            | Symbol               | Test Conditions                            | Min  | Тур  | Max  | Unit |  |  |

|------------------------------------------------------|----------------------|--------------------------------------------|------|------|------|------|--|--|

| VDD Section                                          |                      |                                            |      |      |      |      |  |  |

| VDD OVP Threshold Voltage                            | V <sub>OVP</sub>     |                                            | 25.5 | 27   | 28.5 | V    |  |  |

| VDD OVP De-bounce Time                               |                      |                                            |      | 10   |      | μS   |  |  |

| VDD On Threshold Voltage                             | V <sub>ON_TH</sub>   |                                            | 15   | 16   | 17   | V    |  |  |

| VDD Off Threshold Voltage                            | V <sub>OFF_TH</sub>  |                                            | 8    | 9    | 10   | V    |  |  |

| Zener Voltage                                        | VZ                   |                                            | 29   |      |      | ٧    |  |  |

| Operating Supply Current                             | I <sub>DD_OP</sub>   | I <sub>ZCD</sub> = 0, @ GATE = open, 70kHz |      |      | 2.5  | mA   |  |  |

| Quiescent Current                                    | lQ                   | Turn on in burst mode @ gate open          |      |      | 1.7  | mA   |  |  |

| Standby Current                                      |                      | PFC is disabled                            |      |      | 0.6  | mA   |  |  |

| Start-Up Current                                     | I <sub>DD_ST</sub>   | Before V <sub>ON_TH</sub>                  |      |      | 20   | μΑ   |  |  |

| ZCD Section                                          | ZCD Section          |                                            |      |      |      |      |  |  |

| Upper Clamp Voltage                                  | V <sub>ZC_DH</sub>   | I <sub>ZCD</sub> = 2.5mA                   | 4.5  | 4.8  | 5.5  | V    |  |  |

| Lower Clamp Voltage                                  | V <sub>ZC_DL</sub>   | $I_{ZCD} = -2.5 \text{mA}$                 | 0.3  | 0.65 | -    | ٧    |  |  |

| Arming Voltage                                       | V <sub>ZC_DA</sub>   | (Note 5)                                   |      | 1.6  |      | V    |  |  |

| Trigger Voltage                                      | V <sub>ZC_DT</sub>   | (Note 5)                                   |      | 1    |      | V    |  |  |

| Delay Time Between Trigger<br>Point and Gate Turn On |                      |                                            |      | 100  | 170  | ns   |  |  |

| ZCD Time-Out                                         | T <sub>ZC_TOUT</sub> |                                            |      | 4    |      | μS   |  |  |

| Sourcing Current Capability                          |                      |                                            | -2.5 |      | -6.5 | mA   |  |  |

| Sinking Current Capability                           |                      |                                            | 2.5  |      |      | mA   |  |  |

| Parameter                    |               | Symbol                | Test Conditions                                                               |      | Тур  | Max   | Unit          |  |

|------------------------------|---------------|-----------------------|-------------------------------------------------------------------------------|------|------|-------|---------------|--|

| Disable Voltage              |               | V <sub>ZCD_DIS</sub>  |                                                                               |      |      | 250   | mV            |  |

| Restart Voltage              |               | V <sub>ZCD_EN</sub>   |                                                                               | 1    |      |       | V             |  |

| Pull-High Current            | After Disable |                       |                                                                               | 30   | 75   | 100   | μА            |  |

| FF Section                   |               |                       |                                                                               | •    |      |       | •             |  |

| Input Bias Current           |               | I <sub>BIAS</sub>     | Leakage Current of FF Pin                                                     |      |      | 1     | μА            |  |

| Brown-In Threshol            | d             | V <sub>BR_IN</sub>    |                                                                               | 1.04 | 1.1  | 1.16  | V             |  |

| Brown-Out Thresh             | old           | V <sub>BR</sub> OUT   |                                                                               |      | 0.6  | 0.65  | V             |  |

| Brown-In/Out De-b            | ounce Time    |                       |                                                                               | 40   | 80   | 150   | μS            |  |

| GM Section                   |               | •                     | •                                                                             |      |      | I     |               |  |

| Non-Inverting Inpu           | ıt Reference  | V <sub>REF</sub>      | Including Offset, Full VDD Range,<br>T <sub>A</sub> = 25°C                    |      | 2.5  | 2.525 | V             |  |

| INV Bias Current             |               |                       |                                                                               |      | -    | -1    | μА            |  |

| Transconduction              |               | gm                    | If  V <sub>ERROR</sub>   < 0.25V                                              | 80   | 100  | 120   | μ <b>A</b> /V |  |

| Non-linear Gm                |               |                       | Otherwise                                                                     |      | 1    |       | mA            |  |

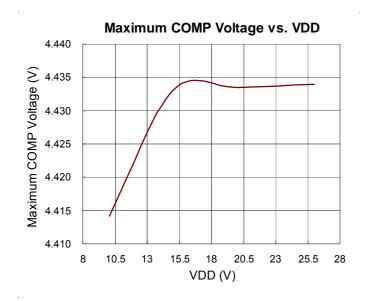

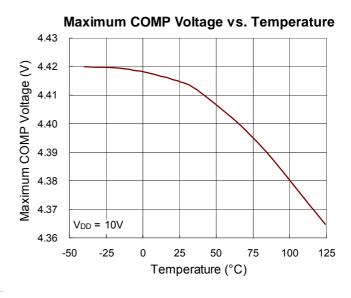

| COMP Maximum \               | √oltage       | VCOMP_OP              |                                                                               |      |      |       | V             |  |

| PWM Section                  |               |                       |                                                                               |      |      | !     | ļ             |  |

| INV OVP Threshol             | ld Voltage    |                       |                                                                               | 2.65 | 2.75 | 2.85  | V             |  |

| INV UVP Threshol             | d Voltage     |                       |                                                                               | 0.3  | 0.4  | 0.5   | V             |  |

| INV OVP/UVP De-              | -bounce Time  |                       |                                                                               |      | 20   |       | μS            |  |

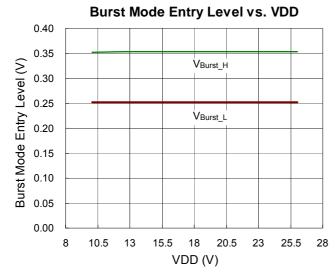

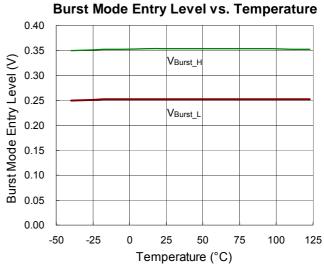

| D Mada Fata                  | Level High    | V <sub>BURST_</sub> H | Measure at COMP Pin                                                           | 0.3  | 0.35 | 0.4   | - V           |  |

| Burst Mode Entry             | Level Low     | V <sub>BURST_L</sub>  | Measure at COMP Pin                                                           | 0.2  | 0.25 | 0.3   |               |  |

| De-bounce Time of            | of Burst Mode |                       |                                                                               | 1.5  | 2    | 4     | μS            |  |

| Ramp Charging C              | urrent        | gm <sub>RAMP</sub>    |                                                                               | 2.15 | 2.5  | 2.85  | μ <b>A</b> /V |  |

| Minimum On-Time              | )             |                       | $T_{ON(MIN)\_PFC}$ = 3pF x 2.5V / ( $I_{ZCD}$ x 0.02), $I_{ZCD}$ = 75 $\mu$ A |      | 5.4  | 6.4   | μS            |  |

| Current Sense Se             | ection        |                       |                                                                               |      |      |       |               |  |

| Leading Edge Blar            | nking Time    | T <sub>LEB_PFC</sub>  | LEB + Delay (Note 6)                                                          | 240  | 400  | 570   | ns            |  |

| Current Sense Thr<br>Voltage | eshold        | Vcs_pfc               |                                                                               |      | 0.4  | 0.45  | V             |  |

| Gate Driver Secti            | on            |                       |                                                                               |      |      |       |               |  |

| Rising Time                  |               | T <sub>R</sub>        | C <sub>L</sub> = 1nF                                                          |      | 40   | 80    | ns            |  |

| Falling Time                 |               | T <sub>F</sub>        | C <sub>L</sub> = 1nF                                                          |      | 30   | 70    | ns            |  |

| Gate Output Clamping Voltage |               | VCLAMP                | V <sub>DD</sub> = 25V                                                         |      | 13   |       | V             |  |

| Internal Pull Low Resistor   |               |                       |                                                                               |      | 12   |       | kΩ            |  |

| Oscillator Section           | 1             |                       |                                                                               |      |      |       |               |  |

| Valley Mask Time             |               | T <sub>MASK</sub>     |                                                                               | 7    | 8.5  | 10    | μS            |  |

| Duration of Starter          |               | T <sub>START</sub>    |                                                                               | 75   | 130  | 300   | μS            |  |

| Maximum On-Time              |               |                       | Maximum T <sub>ON(MAX)_PFC</sub>                                              |      |      |       |               |  |

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

- Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a low effective thermal conductivity single-layer test board per JEDEC 51-3.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Guaranteed by Design.

- Note 6. Leading edge blanking time and internal propagation delay time is guaranteed by design.

www.richtek.com

# **Typical Application Circuit**

## Typical Application Circuit for Boost PFC Pre-Regulator

### Typical Application Circuit for Single Stage PFC Converter

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Typical Operating Characteristics**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Application Information**

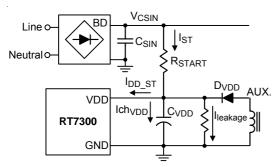

### Start-Up Circuit Design

Figure 13. Start-Up Circuit

Figure 14. Start-Up Waveforms of VDD and IDD

Figure 13 and Figure 14 show the equivalent start-up circuit and VDD waveform during start-up. In general, the startup time (t<sub>start</sub>) is required from system specification. The charging current (Ich<sub>VDD</sub>) can be estimated by the following equation.

$$Ich_{VDD} = \frac{C_{VDD} \times V_{ON\_TH}}{t_{start}}$$

(10)

where C<sub>VDD</sub> is the capacitor connected between VDD and GND, V<sub>ON\_TH</sub> is the power on threshold (16V typ.).

The start-up resistor (R<sub>start</sub>) connected between V<sub>CSIN</sub> and VDD should be able to support the charging current (Ich<sub>VDD</sub>), start-up current (I<sub>DD</sub> <sub>ST</sub>) and leakage current  $(I_{leakage})$  of  $C_{VDD}$  before the VDD is supported by the auxiliary winding. The maximum start-up resistance can be calculated by the equation (11).

$$R_{Start} = \frac{\sqrt{2} \times V_{BNO}}{I_{DD\_ST} + I_{ChVDD} + I_{leakage}}$$

(11)

where V<sub>BNO</sub> is the Brown-out voltage. Note that the startup resistor must have adequate voltage rating for reliability. 2 resistors in series can be applied for most of applications.

For example, the system required start-up time is 3sec,  $V_{BNO}$  = 75V and maximum  $I_{DD}$  ST = 20 $\mu$ A. If  $C_{VDD}$  = 22 $\mu$ F is selected and the leakage current of C<sub>VDD</sub> can be ignored, the start-up resistor should be less than  $772k\Omega$ .

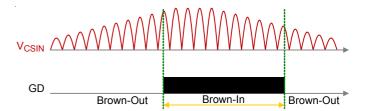

#### **Brown-In and Brown-Out**

The FF pin is used for the detection of Brown-in and Brownout functions to protect converter from over stress at low input voltage situation. A proper voltage divider should be applied to sense the line voltage after bridge diode rectifier shown as Figure 15.

Figure 15. Brown-In/Brown-Out Application Circuit

Figure 16. Brown-In/Brown-Out Waveform

The Brown-in threshold voltage at FF pin is set at 1.1V. In other words, the controller will be active when the input voltage increases to be higher than the threshold voltage. Once the Brown-in voltage (V<sub>BNI</sub> in rms) is decided, the resistor R<sub>FF1</sub> and R<sub>FF2</sub> can be estimated by the equation (12). For the noise immunity and power saving consideration,  $R_{FF2}$  is suggested to be around  $100k\Omega$ .

$$\frac{\mathsf{RFF1}}{\mathsf{RFF2}} \le \frac{\sqrt{2} \times \mathsf{V_{BNI}}}{1.1\mathsf{V}} - 1 \tag{12}$$

The capacitor  $C_{FF}$  is applied to filter out the input ripple voltage. The corner frequency should be lower than line frequency ( $f_{line}$ ). If the FF pin voltage is not flat, the PF and THD performance will be degraded.

$$\frac{1}{2\pi \times (R_{FF1} // R_{FF2}) \times C_{FF}} < 0.1 \times f_{line}$$

(13)

## **Boost Inductance Design**

Differ from the traditional transient mode PFC, the Boost inductor design is based on the RT7300 internal parameters and the parameter "S".

$$S = \frac{R_{FF1} + R_{FF2}}{R_{FF2}} \tag{14}$$

Assume the maximum input power is Pin, the inductance of the Boost inductor can be derived as following equations.

$$\begin{split} I_{L\_pk} &= 2 \times \frac{P_{in}}{V_{IN(MN)}} \times \sqrt{2} \\ &= \frac{\sqrt{2} \times V_{IN(MIN)}}{L_{PFC}} \times \frac{V_{COMP} \times C_{Ramp}}{0.5 \times gm_{Ramp} \times \left(\frac{\sqrt{2} \times V_{IN(MIN)}}{S} \times \frac{2}{\pi}\right)^2} \end{split}$$

$$L_{PFC} = \frac{\pi^2 \times m \times V_{COMP\_OP} \times C_{Ramp} \times S^2}{8 \times P_{in} \times g m_{Ramp}}$$

$$= \frac{m \times S^2}{P_{in}} \times 13.63 \quad (\mu H)$$

(15)

where "m" is the ratio of  $V_{Comp}/V_{Comp\_op}$  which is the derating factor of the maximum power. It's suggested to use 0.6 to 0.9 for the m factor.

### **Current Limit Setting**

The maximum current of the power MOSFET is limited by the current sense resistor between the CS pin and GND. The threshold voltage at CS pin is 0.4V typically. The current sense resistor can be calculated by the equation (16) with the peak current of MOSFET.

$$R_{CS} = \frac{0.4V \times 80\%}{I_{L_pk}} \tag{16}$$

#### **Zero Current Detection**

The zero current of inductor is detected from the auxiliary winding shown as typical application circuit. The  $R_{ZCD}$  is used to limit the current into ZCD pin to be lower than 2.5mA. Thus, the  $R_{ZCD}$  is determined by the equation as below.

$$R_{ZCD} > \frac{V_{OUT}}{N \times 2.5 mA} \tag{17}$$

where  $V_{OUT}$  is the output voltage of the PFC converter and N is the turn ratio of auxiliary winding and Boost inductor.

#### **MOSFET Selection**

The RT7300 is designed to operate using an external N-channel power MOSFET. Important parameters for the power MOSFET are breakdown voltage (BV<sub>DSS</sub>), threshold voltage (V<sub>GS\_TH</sub>), on-resistance (R<sub>DS(ON)</sub>), total gate charge (Qg) and maximum current (I<sub>D(MAX)</sub>). The gate driver voltage is from VDD and clamped under 13V typically. Lower Qg characteristics results in lower power losses and lower R<sub>DS(ON)</sub> results in higher efficiency. For high voltage application, it is important to select a device with low gate charge and balance the power consumption between switching loss and conduction loss.

#### **Diode Selection**

Since there is no reverse recovery loss of diode when converter operates in CRM, the diode choosing is based on reverse voltage, forward current and switching speed.

$$I_{D(RMS)} = I_{L_pk} \times \sqrt{\frac{\sqrt{2} \times V_{IN(MIN)}}{\pi \times V_{OUT}}}$$

(18)

$$V_{D(PK)} = V_{OUT} \tag{19}$$

### **Output Capacitor Selection**

The hold-up time and output voltage ( $V_{OUT}$ ) are the major requirements for determining the output capacitance. The narrow  $V_{OUT}$  range can improve the efficiency of DC/DC converter in next power stage. Lower ESR can reduce the power loss of PFC converter and get longer lifetime.

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

$$C_{OUT(MIN)} = \frac{2 \times P_{IN} \times \eta \times T_{Holdup}}{V_{OUT}^2 \times V_{OUT(MIN)}^2}$$

(20)

$I_{C(RMS)} =$

$$\sqrt{I_{L_pk}^2 \times \frac{\sqrt{2} \times V_{IN(MAX)}}{\pi \times V_{OUT}}} - \left(\frac{\eta P_{IN}}{V_{OUT}}\right)^2 + \left(\text{ac RMS load current}\right)^2}$$

(21)

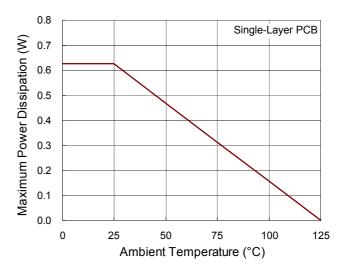

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOP-8 package, the thermal resistance, θ<sub>JA</sub>, is 160°C/W on a standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (160^{\circ}C/W) = 0.625W$$

for SOP-8 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 17 allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 17. Derating Curve of Maximum Power Dissipation

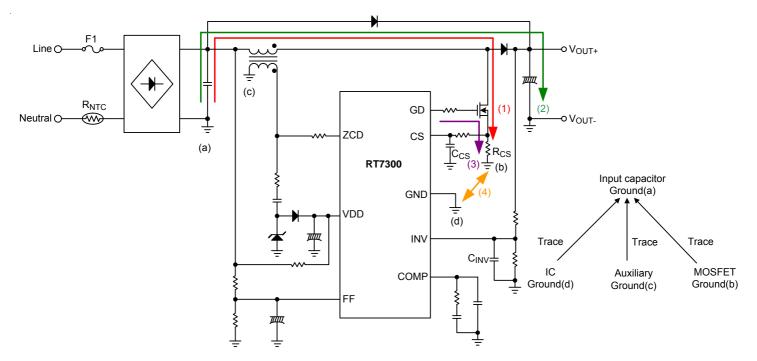

### **Layout Considerations**

A proper PCB layout can abate unknown noise interference and EMI issue in the switching power supply. Please refer to the guidelines when designing a PCB layout for switching power supply.

▶ The current path(1) from input capacitor, inductor, MOSFET, R<sub>CS</sub> return to input capacitor and the current path(2) from input capacitor, inductor, output diode, output filter capacitor return to input capacitor are high frequency current loops. The path(3) from GD pin, MOSFET, R<sub>CS</sub> to ground is also a high frequency current loop. They must be as short as possible to decrease noise coupling and kept a space to other low voltage traces, such as IC control circuit paths, especially. Besides, the path(4) between MOSFET ground(b) and IC ground(d) is recommended to be as short as possible, too.

It is good for reducing noise, output ripple and EMI issue to separate ground traces of input capacitor(a), MOSFET(b), auxiliary winding(c) and IC control circuit(d). Finally, connect them together on input capacitor ground(a). The areas of these ground traces should be kept large.

Placing bypass capacitor for abating noise on IC is highly recommended. The capacitors C<sub>INV</sub> and C<sub>CS</sub> should be placed as close to controller as possible.

In addition, apply sufficient copper area at the anode and cathode terminal of the diode for heat-sinking. It is recommended to apply a larger area at the quiet cathode terminal. A large anode area will induce high-frequency radiated EMI.

Figure 18. PCB Layout Guide

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

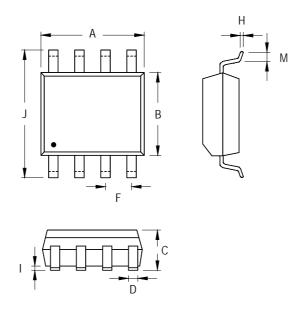

## **Outline Dimension**

| O. mak al | Dimensions I | In Millimeters | Dimensions In Inches |       |  |

|-----------|--------------|----------------|----------------------|-------|--|

| Symbol    | Min          | Max            | Min                  | Max   |  |

| А         | 4.801        | 5.004          | 0.189                | 0.197 |  |

| В         | 3.810        | 3.988          | 0.150                | 0.157 |  |

| С         | 1.346        | 1.753          | 0.053                | 0.069 |  |

| D         | 0.330        | 0.508          | 0.013                | 0.020 |  |

| F         | 1.194        | 1.346          | 0.047                | 0.053 |  |

| Н         | 0.170        | 0.254          | 0.007                | 0.010 |  |

| I         | 0.050        | 0.254          | 0.002                | 0.010 |  |

| J         | 5.791        | 6.200          | 0.228                | 0.244 |  |

| M         | 0.400        | 1.270          | 0.016                | 0.050 |  |

8-Lead SOP Plastic Package

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.