### **Features**

- High Output Current: 2A Source/4A Sink

- Wide Operating Voltage Range: -10V to +26V

- Negative Gate Drive Capability

- · Desaturation Detection Circuit

- Separate Source and Sink Outputs

- Programmable Blanking and Output Tristate

- TTL Compatible Inputs

- -40°C to +125°C Extended Operating Temperature Range

- Under-Voltage Lockout Circuitry

- Fault Status Output

# **Applications**

- · Efficient IGBT Switching

- Motor Controls

- Switch Mode Power Supplies

# **Description**

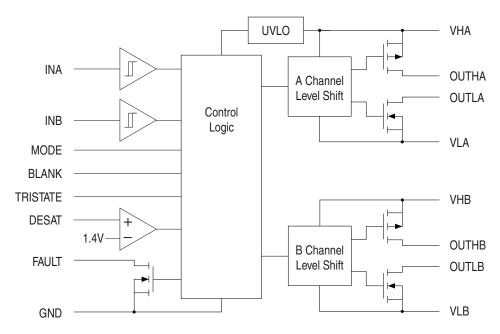

The IX2204 is a dual high current gate driver specifically designed to drive the gates of high current IGBTs. The IX2204 provides two high current outputs capable of sourcing 2A and sinking 4A. The outputs can be paralleled for IGBT gates that require higher drive current. The outputs have a wide operating voltage range, and are able to provide a negative gate drive voltage to ensure the turn-off of high power IGBTs. A desaturation detection circuit protects the power IGBT during a short circuit. The IX2204 has a programmable two-level turn-off feature that protects the device against excessive voltages when the IGBT is being turned off due to an over-current situation.

The IX2204 has under voltage lockout circuitry and a fault status output, and is available in a 16-lead thermally enhanced SOIC package.

# **Ordering Information**

| Part       | Description                            |

|------------|----------------------------------------|

| IX2204NE   | 16-Pin SOIC in Tubes (50/Tube)         |

| IX2204NETR | 16-Pin SOIC in Tape & Reel (2000/Reel) |

### **IX2204 Functional Block Diagram**

| 1. Specifications                                     |

|-------------------------------------------------------|

| 1.1 Package Pinout: 16-Pin SOIC Package               |

| 1.2 Pin Description: 16-Pin SOIC Package              |

| 1.3 Absolute Maximum Ratings4                         |

| 1.4 Recommended Operating Conditions                  |

| 1.5 DC Electrical Characteristics                     |

| 1.6 AC Electrical Characteristics                     |

| 1.7 Thermal Characteristics 5                         |

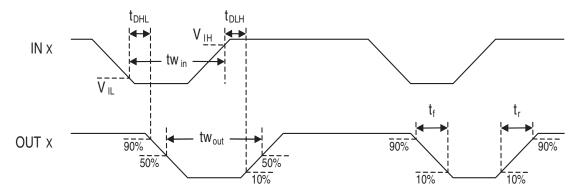

| 1.8 AC Input/Output Timing Diagram (MODE=0V)          |

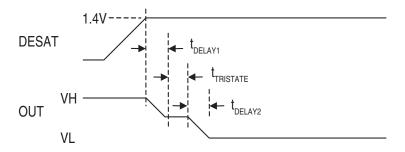

| 1.9 AC Fault Timing Diagram                           |

| O. Bandannana Ohansataniatiaa                         |

| 2. Performance Characteristics                        |

| 3. Functional Description                             |

| 3.1 Input                                             |

| 3.2 Mode                                              |

| 3.3 Desaturation Protection                           |

| 3.4 Under-Voltage Protection                          |

| 3.5 Fault Output                                      |

| 3.6 Outputs 7                                         |

| A Application Durantons                               |

| 4. Application Drawings                               |

|                                                       |

| 4.2 Direct IGBT Drive                                 |

| 4.3 Stack-wode IGBT Drive with Desaturation Detection |

| 5. Manufacturing Information                          |

| 5.1 Moisture Sensitivity                              |

| 5.2 ESD Sensitivity                                   |

| 5.3 Soldering Profile                                 |

| 5.4 Board Wash 9                                      |

| 5.5 Mechanical Dimensions                             |

# 1 Specifications

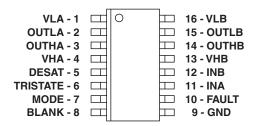

# 1.1 Package Pinout: 16-Pin SOIC Package

# 1.2 Pin Description: 16-Pin SOIC Package

| Pin# | Name     | Description                              |  |

|------|----------|------------------------------------------|--|

| 1    | VLA      | Channel A negative supply                |  |

| 2    | OUTLA    | Channel A sinking output                 |  |

| 3    | OUTHA    | Channel A sourcing output                |  |

| 4    | VHA      | Channel A positive supply & logic supply |  |

| 5    | DESAT    | Desaturation comparator input            |  |

| 6    | TRISTATE | Channel A tristate timing                |  |

| 7    | MODE     | Mode control                             |  |

| 8    | BLANK    | Channel A start-up blanking time         |  |

| 9    | GND      | Signal ground                            |  |

| 10   | FAULT    | Fault status output                      |  |

| 11   | INA      | Channel A logic input                    |  |

| 12   | INB      | Channel B logic input                    |  |

| 13   | VHB      | Channel B positive Supply                |  |

| 14   | OUTHB    | Channel B sourcing output                |  |

| 15   | OUTLB    | Channel B sinking output                 |  |

| 16   | VLB      | Channel B negative supply                |  |

# 1.3 Absolute Maximum Ratings

| Parameter                      | Symbol            | Minimum | Maximum | Units |

|--------------------------------|-------------------|---------|---------|-------|

| VH Supply Voltage <sup>1</sup> | VHA, VHB          | -       | 26      | V     |

| VL Supply Voltage              | VLA, VLB          | -10     | -       | V     |

| Supply Voltage All Other Pins  | -                 | GND-0.3 | VHA+0.3 | V     |

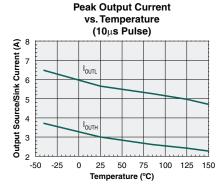

| Output Sourcing Current        | l <sub>outh</sub> | -       | -2      | Α     |

| Output Sinking Current         | I <sub>OUTL</sub> | -       | 4       | Α     |

| Junction Temperature           | TJ                | -55     | +150    | °C    |

| Storage Temperature            | T <sub>STG</sub>  | -65     | +150    | °C    |

Note 1: VHx-VLx maximum is 26V.

# 1.4 Recommended Operating Conditions

| Parameter                   | Symbol         | Minimum | Maximum | Units |

|-----------------------------|----------------|---------|---------|-------|

| VH Supply Voltage           | VHA, VHB       | -       | 25      | V     |

| VL Supply Voltage           | VLA, VLB       | -10     | GND     | V     |

| Operating Temperature Range | T <sub>A</sub> | -40     | +125    | °C    |

# 1.5 DC Electrical Characteristics

$13V \le VHA \le 25V$ ;  $13V \le VHB \le 25V$ ;  $-40^{\circ}C \le T_A \le 125^{\circ}C$ .

| Parameter                                     | Conditions                         | Symbol              | Minimum  | Typical | Maximum  | Units |

|-----------------------------------------------|------------------------------------|---------------------|----------|---------|----------|-------|

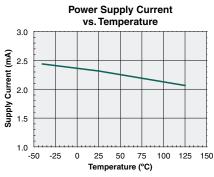

| Power Supply Current                          | VHA=18V                            | I <sub>VHA</sub>    | -        | -       | 3.5      | mA    |

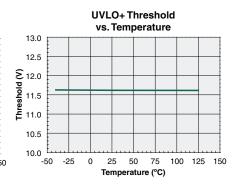

| Under-Voltage Lockout Output Enable Threshold | VHA Rising                         | UVLO+               | 10       | -       | 13       | V     |

| Under-Voltage Lockout Output Hysteresis       | -                                  | UVLO <sub>HYS</sub> | -        | 1       | -        | V     |

| INA / INB Logic Low Threshold                 | -                                  | $V_{IL}$            | 0.8      | -       | -        | V     |

| INA / INB Logic High Threshold                | -                                  | V <sub>IH</sub>     | -        | -       | 2        | ٧     |

| INA / INB / MODE Input Current                | -                                  | I <sub>IN</sub>     | -        | -       | 1        | μΑ    |

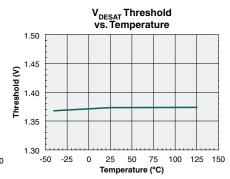

| DESAT Threshold                               | -                                  | V <sub>DESAT</sub>  | 1.26     | 1.4     | 1.54     | V     |

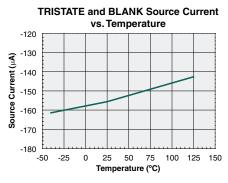

| TRISTATE / BLANK Source Current               | -                                  | I <sub>SRC</sub>    | -100     | -160    | -210     | μΑ    |

| FAULT Output                                  |                                    |                     |          |         |          |       |

| FAULT Low Voltage                             | I <sub>FAULT</sub> =8mA            | V <sub>FAULT</sub>  | -        | -       | 0.8      | V     |

| Outputs                                       |                                    | 1                   | -        |         |          |       |

| Low Output Voltage                            | No Load                            | V <sub>OUTL</sub>   | -        | -       | VL+0.025 | V     |

| High Output Voltage                           | No Load                            | V <sub>OUTH</sub>   | VH-0.025 | -       | -        | V     |

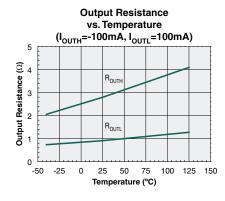

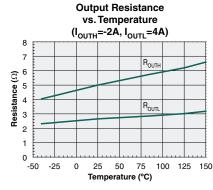

| Output Resistance                             | VH=18V, I <sub>OUTH</sub> = -100mA | R <sub>OUTH</sub>   | -        | 2.4     | 5        | Ω     |

| Output Hesistance                             | VH=18V, I <sub>OUTL</sub> = 100mA  | R <sub>OUTL</sub>   | -        | 1.2     | 2        | Ω     |

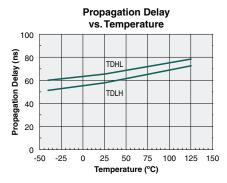

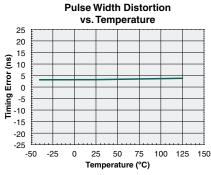

## 1.6 AC Electrical Characteristics

$13V \leq VHA \leq 25V$ ;  $-40^{\circ}C \leq T_A \leq 125^{\circ}C$

| Parameter                            | Conditions                                                      | Symbol              | Minimum | Typical | Maximum | Units |

|--------------------------------------|-----------------------------------------------------------------|---------------------|---------|---------|---------|-------|

| OUT Rise Time                        |                                                                 | t <sub>r</sub>      | -       | -       | 40      |       |

| OUT Fall Time                        | VH=18V, C <sub>I OAD</sub> =1nF                                 | t <sub>f</sub>      | -       | 8       | 20      | ns    |

| Delay, IN to OUT Rising              |                                                                 | TDLH                | -       | 70      | 100     | 110   |

| Delay, IN to OUT Falling             |                                                                 | TDHL                | -       | 70      | 100     |       |

| IN to OUT Pulse Distortion           | (tw <sub>in</sub> - tw <sub>out</sub> ), C <sub>LOAD</sub> =0   | Δtw                 | -       | 7       | 25      | ns    |

| III to OOT Fuise Distortion          | (tw <sub>in</sub> - tw <sub>out</sub> ), C <sub>LOAD</sub> =1nF |                     | -       | 7       | 25      |       |

| DESAT Blank Time                     | C <sub>BLANK</sub> =0                                           | t                   | -       | -       | 100     | ns    |

| DEGAL BIAIR TIME                     | C <sub>BLANK</sub> =100pF                                       | t <sub>BLANK</sub>  | -       | 875     | -       |       |

| Delay Time, DESAT to Output Tristate | $R_L$ =100 $\Omega$ to GND                                      | t <sub>DELAY1</sub> | -       | 50      | 100     | ns    |

| Duration of Tristate OUT             | C <sub>TRISTATE</sub> =0                                        | trojorare           | -       | -       | 100     | nc    |

| Duration of motito oo i              | C <sub>TRISTATE</sub> =100pF                                    | TRISTATE            | -       | 1000    | -       | ns    |

| Delay Time, TRISTATE high to OUT Low | VH=18V, C <sub>LOAD</sub> =1nF                                  | t <sub>DELAY2</sub> | -       | -       | 100     | ns    |

## 1.7 Thermal Characteristics

| Parameter                               | Symbol            | Rating | Units |

|-----------------------------------------|-------------------|--------|-------|

| Thermal Resistance, Junction to Ambient | $\theta_{\sf JA}$ | 75.4   | °C/W  |

# 1.8 AC Input/Output Timing Diagram (MODE=0V)

# 1.9 AC Fault Timing Diagram

## 2 Performance Characteristics

# 3 Functional Description

### 3.1 Input

The INA and INB inputs are TTL compatible and must be referenced to GND.

#### 3.2 Mode

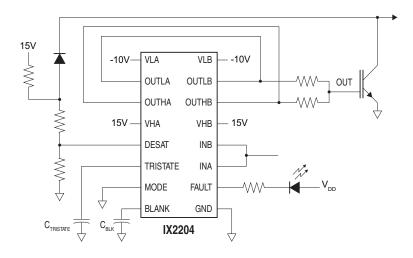

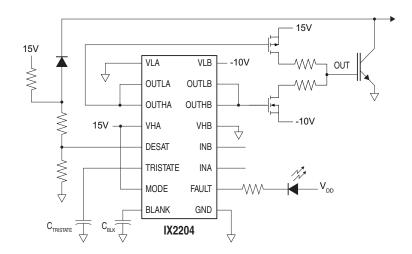

The MODE input determines how the desaturation protection and Under-Voltage Lock Out (UVLO) protection circuitry controls the OUTHA, OUTLA, OUTHB and OUTLB outputs. For parallel-mode IGBT drive, MODE should be connected to GND (see 4.1). For driving IGBTs that require higher gate drive current than the IX2204 can provide, the IX2204 can be used to control external drive transistors. In this stacked configuration, the external drive transistors constitute an inverting stage, and MODE should be connected to VHA for proper desaturation protection and UVLO operation (see 4.3).

#### 3.3 Desaturation Protection

The desaturation protection circuit ensures the protection of an external IGBT in the event of an over-current situation. When the voltage at DESAT exceeds 1.4V (typically) and MODE is connected to GND, OUTLA and OUTLB are driven low in a two-step process. First OUTLA, OUTHA, OUTLB and OUTHB are all turned off (high impedance). Then after a programmable time (t<sub>TRISTATE</sub>), both OUTLA and OUTLB are turned on (driven low), which quickly turns off the IGBT. This two-step action avoids both dangerous over-voltages across the IGBT and reverse-bias SOA problems, especially during a short circuit turn-off. The time that all the outputs are in tristate is set by an internal current source and an external capacitor (CTRISTATE) that is connected to the TRISTATE pin. The tristate time is approximately:

The desaturation circuit is disabled for a fixed blanking time to avoid detecting a false desaturation event during IGBT turn-on, thus allowing enough time for IGBT saturation. This blanking time is set by an internal current source and an external capacitor,  $C_{BLK}$ . The blanking time is approximately:

$$t_{BIK} = 8750 \cdot C_{BIK}$$

This blanking time starts when INA transitions from low to high.

The desaturation two-step turn off is slightly different when MODE is connected to VHA for stack-mode IGBT drive. When the DESAT voltage exceeds 1.4V, OUTHA and OUTLB are turned on, tristating the IGBT. After the t<sub>TRISTATE</sub> time, OUTHA and OUTLB are turned off, and OUTHB is turned on, which in conjunction with the external drive transistor quickly turns off the IGBT. When MODE is connected to VHA, the blanking time starts when INA transitions from high to low.

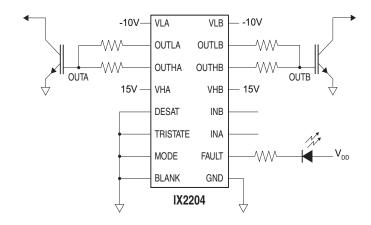

The desaturation protection circuit cannot be used when the IX2204 is used to drive two separate IGBTs (direct IGBT drive, see 4.2). When driving two separate IGBTs, the DESAT, TRISTATE, MODE, and BLANK pins should all be connected to GND.

### 3.4 Under-Voltage Protection

The Under Voltage Lock Out (UVLO) circuit protects the IGBT from insufficient gate voltage. The UVLO circuit monitors the VHA supply voltage. If MODE is connected to GND and VHA is below the UVLO+ threshold, OUTHA and OUTHB are both turned-off (high impedance), and both OUTLA and OUTLB are both turned on (pulled low). If VHA is below the UVLO+ threshold and MODE is connected to VHA, OUTHA and OUTHB are both are turned on, and OUTLA and OUTLB are both turned off.

| Table 2: Output States with VHA < UVLO+ |       |       |       |       |  |

|-----------------------------------------|-------|-------|-------|-------|--|

| Mode                                    | OUTHA | OUTLA | OUTHB | OUTLB |  |

| GND                                     | Z     | 0     | Z     | 0     |  |

| VHA                                     | 1     | Z     | 1     | Z     |  |

### 3.5 Fault Output

The FAULT output is pulled low during a desaturation event, or when VHA is below UVLO+.

## 3.6 Outputs

The output stages are able to source 2A, and sink 4A. Separated sink and source outputs allow independent gate charge and discharge control. For higher gate drive applications, the source and sink outputs can be paralleled to source 4A, and sink 8A.

# 4 Application Drawings

## 4.1 Parallel-Mode IGBT Drive with Desaturation Detection

### **4.2 Direct IGBT Drive**

## 4.3 Stack-Mode IGBT Drive with Desaturation Detection

# 5 Manufacturing Information

### 5.1 Moisture Sensitivity

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. IXYS Integrated Circuits Division classified all of its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard, IPC/JEDEC J-STD-020, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard as well as to any limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a **Moisture Sensitivity Level (MSL) rating** as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device   | Moisture Sensitivity Level (MSL) Rating |

|----------|-----------------------------------------|

| IX2204NE | MSL 1                                   |

### 5.2 ESD Sensitivity

This product is **ESD Sensitive**, and should be handled according to the industry standard **JESD-625**.

### 5.3 Soldering Profile

This product has a maximum body temperature and time rating as shown below. All other guidelines of **J-STD-020** must be observed.

| Device   | Maximum Temperature x Time | Maximum Reflow Cycles |

|----------|----------------------------|-----------------------|

| IX2204NE | 260°C for 30 seconds       | 3                     |

### 5.4 Board Wash

IXYS Integrated Circuits Division recommends the use of no-clean flux formulations. However, board washing to remove flux residue is acceptable, and the use of a short drying bake may be necessary. Chlorine-based or Fluorine-based solvents or fluxes should not be used. Cleaning methods that employ ultrasonic energy should not be used.

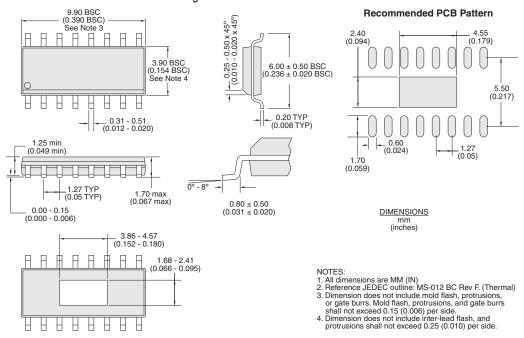

#### 5.5 Mechanical Dimensions

### 5.5.1 IX2204NE 16-Pin Narrow SOIC Package

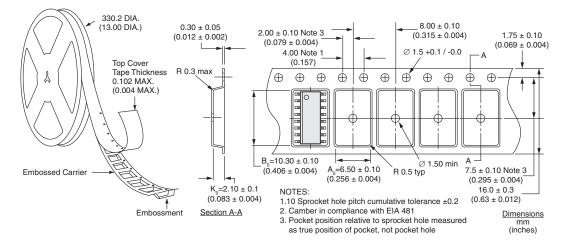

### 5.5.2 IX2204NETR Tape & Reel Packaging for 16-Pin Narrow SOIC Package (TBD)

## For additional information please visit our website at: www.ixysic.com

IXYS Integrated Circuits Division makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. Neither circuit patent licenses nor indemnity are expressed or implied. Except as set forth in IXYS Integrated Circuits Division's Standard Terms and Conditions of Sale, IXYS Integrated Circuits Division assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

The products described in this document are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or where malfunction of IXYS Integrated Circuits Division's product may result in direct physical harm, injury, or death to a person or severe property or environmental damage. IXYS Integrated Circuits Division reserves the right to discontinue or make changes to its products at any time without notice.

Specification: DS-IX2204-R03 ©Copyright 2014, IXYS Integrated Circuits Division All rights reserved. Printed in USA. 11/11/2014