# **Precision Digital Power Monitor with Margining**

# ISL28023

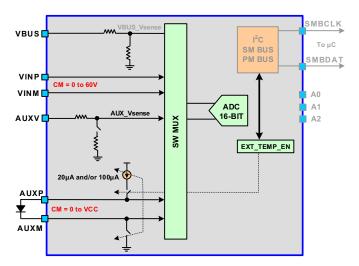

The ISL28023 is a bidirectional high-side and low-side digital current sense and voltage monitor with a serial interface. The device monitors power supply current, voltage and provides the digital results along with calculated power. The ISL28023 provides tight accuracy of 0.05% for both voltage and current monitoring. The auxiliary input provides an additional power monitor function.

The  $V_{CC}$  power can either be externally supplied or internally regulated, which allows the ISL28023 to handle a common-mode input voltage range from OV to 60V. The wide range permits the device to handle telecom, automotive and industrial applications with minimal external circuitry.

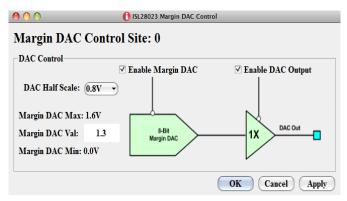

An 8-bit voltage DAC enables a DC/DC converter output voltage margining. Fault indication includes a Bus Voltage window and overcurrent fast fault logic indication.

The ISL28023 serial interface is PMBus compatible and operates down to 1.2V voltage. It draws an average current of just  $800\mu\text{A}$  and is available in the space saving 24 Ld QFN 4mmx4mm package. The part operates across the full industrial temperature range from -40°C to +125°C.

# **Related Literature**

AN1955, "Design Ideas for Intersil Digital Power Monitors"

1

AN1932, "ISL28023 Precision Digital Power Monitor Evaluation Kit"

# **Features**

| • | Bus voltage sense range              | 0V to 60V |

|---|--------------------------------------|-----------|

| • | Voltage gain error                   | 0.05%     |

| • | Current gain error                   | 0.05%     |

| • | Internal temperature sensor accuracy | +1 0°C    |

- . High or low (RTN) side sensing

- · Bidirectional current sensing

- · Auxiliary low voltage channel

- ∆∑ADC, 16-bit native resolution

- · Programmable averaging modes

- · Internal 3.3V regulator

- · Internal temperature sense

- Overvoltage/undervoltage and current fault monitoring with 500ns detection delay

- · 8-bit voltage output DAC

- I<sup>2</sup>C/SMBus/PMBus interface that handles 1.2V supply

# **Applications**

- · Data processing servers

- · DC power distribution

- · Telecom equipment

- · Portable communication equipment

- DC/DC, AC/DC converters

- Many I<sup>2</sup>C DAC and ADC with alert applications

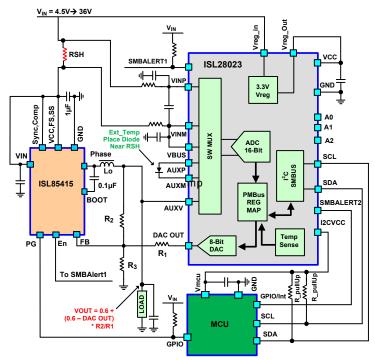

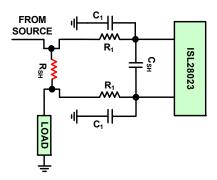

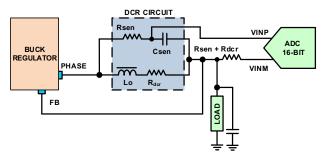

FIGURE 1. APPLICATION DIAGRAM

# **Table of Contents**

| Block Diagram                                             | 3  |

|-----------------------------------------------------------|----|

| Ordering Information                                      | 3  |

| Pin Configuration                                         |    |

| Pin Descriptions.                                         |    |

| Absolute Maximum Ratings                                  |    |

| Thermal Information                                       |    |

|                                                           |    |

| Recommended Operating Conditions                          |    |

| Electrical Specifications                                 |    |

| Typical Performance Curves                                |    |

| Overview                                                  |    |

| Pin Descriptions                                          | 27 |

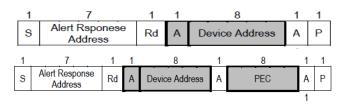

| Communication Protocol                                    | 30 |

| Packet Error Correction (PEC)                             | 30 |

| IC Device Details                                         |    |

| Global IC Controls Primary and Auxiliary Channel Controls |    |

| Measurement Registers                                     |    |

| Threshold Detectors                                       |    |

| SMB Alert                                                 | 38 |

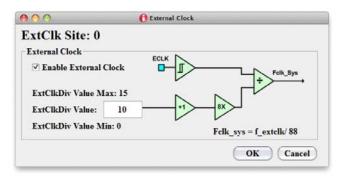

| External Clock Control                                    |    |

| Voltage Margin                                            |    |

| SMBus/I <sup>2</sup> C Serial Interface                   |    |

| Protocol Conventions                                      |    |

| SMBus, PMBus Support                                      |    |

| Device Addressing                                         |    |

| Write Operation                                           |    |

| Read Operation                                            |    |

| Clock Speed                                               |    |

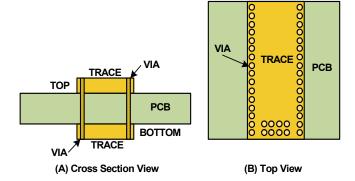

| Signal Integrity                                          | 47 |

| Fast Transients.                                          |    |

| External Clock.                                           |    |

| Overranging                                               | 49 |

| Shunt Resistor Selection.                                 |    |

| Lossless Current Sensing (DCR)                            |    |

| Layout                                                    |    |

| Revision History                                          |    |

| •                                                         |    |

| About Intersil                                            |    |

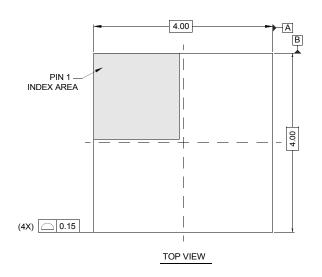

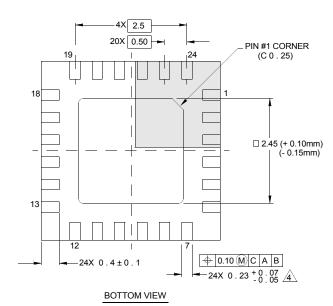

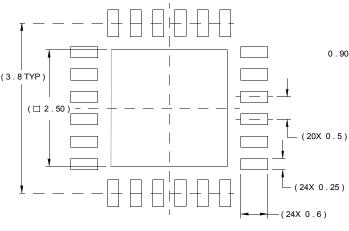

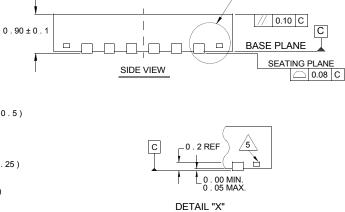

| Package Outline Drawing                                   | 55 |

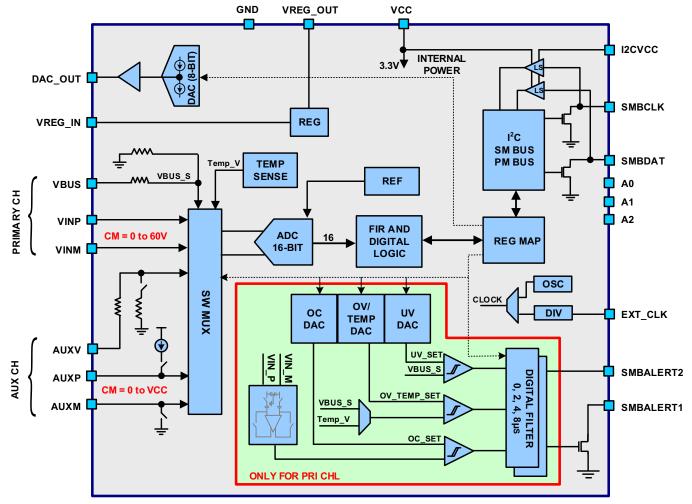

# **Block Diagram**

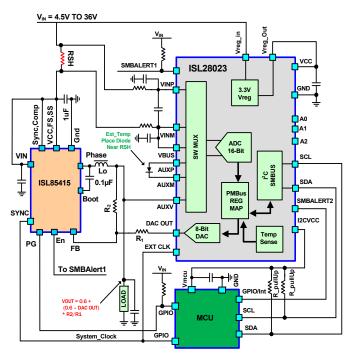

FIGURE 2. BLOCK DIAGRAM

# **Ordering Information**

| PART NUMBER<br>( <u>Notes 1</u> , 2, <u>3</u> ) | PART<br>MARKING  | V <sub>BUS</sub> OPTION<br>(V) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|-------------------------------------------------|------------------|--------------------------------|-----------------------------|----------------|

| ISL28023FR12Z                                   | 280 23R12Z       | 12                             | 24 Ld QFN                   | L24.4x4D       |

| ISL28023FR60Z                                   | 280 23R60Z       | 60                             | 24 Ld QFN                   | L24.4x4D       |

| ISL28023EVAL1Z                                  | Evaluation Board |                                |                             |                |

| ISL28023EVKIT1Z                                 | Evaluation Kit   |                                |                             |                |

### NOTES:

- 1. Add "-T" suffix for 6k unit or "-T7A" suffix for 250 unit Tape and Reel options. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL28023. For more information on MSL please see techbrief TB363.

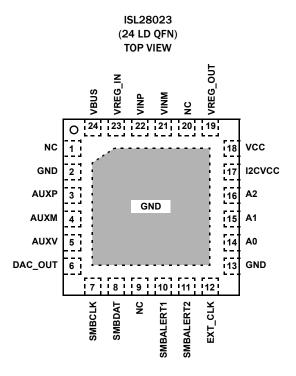

3

# **Pin Configuration**

# **Pin Descriptions**

| PIN NUMBER | PIN NAME  | TYPE/DIR             | PIN DEFINITION                                                                                                     |

|------------|-----------|----------------------|--------------------------------------------------------------------------------------------------------------------|

| 1, 9, 20   | NC        | N/A                  | No connect                                                                                                         |

| 2          | GND       | Power                | Ground                                                                                                             |

| 3          | AUXP      | Analog Input         | Auxiliary port differential input (plus)                                                                           |

| 4          | AUXM      | Analog Input         | Auxiliary port differential input (minus)                                                                          |

| 5          | AUXV      | Analog Input         | Auxiliary port single-ended input                                                                                  |

| 6          | DAC_OUT   | Analog Output        | DAC voltage output                                                                                                 |

| 7          | SMBCLK    | Digital Input        | SMBus/I <sup>2</sup> C clock input                                                                                 |

| 8          | SMBDAT    | Digital Input/Output | SMBus/I <sup>2</sup> C data                                                                                        |

| 10         | SMBALERT1 | Digital Output       | SMBus Alert1, open-drain output                                                                                    |

| 11         | SMBALERT2 | Digital Output       | CPU interrupt signal: It is used as CPU interrupt signal.                                                          |

| 12         | EXT_CLK   | Digital Input        | External ADC clock input                                                                                           |

| 13         | GND       | Power                | Ground                                                                                                             |

| 14         | A0        | Digital Input        | SMBus/I <sup>2</sup> C address input                                                                               |

| 15         | A1        | Digital Input        | SMBus/I <sup>2</sup> C address input                                                                               |

| 16         | A2        | Digital Input        | SMBus/I <sup>2</sup> C address input                                                                               |

| 17         | 12CVCC    | Power                | I <sup>2</sup> C level shifter power supply. This pin should be connected to VCC pin if level shifter is not used. |

| 18         | vcc       | Power                | Chip power supply                                                                                                  |

| 19         | VREG_OUT  | Power                | Voltage regulator output, proper decoupling capacitor should be connected to this pin                              |

| 21         | VINM      | Analog Input         | Current sense minus input                                                                                          |

| 22         | VINP      | Analog Input         | Current sense plus input                                                                                           |

| 23         | VREG_IN   | Power                | Voltage regulator input. This pin should be connected to ground in case voltage regulator is not used.             |

| 24         | VBUS      | Power                | VBUS voltage sense                                                                                                 |

Submit Document Feedback 4 intersil\*

TABLE 1. DPM PORTFOLIO COMPARISON - ISL28022 vs ISL28023 vs ISL28025

|                                  | DESCRIPTION                 | BASIC DIGITAL<br>POWER MONITOR | FULL FEATURE<br>DIGITAL POWER MONITOR | DIGITAL POWER MONITOR IN TINY PACKAGE |  |  |

|----------------------------------|-----------------------------|--------------------------------|---------------------------------------|---------------------------------------|--|--|

|                                  | PART NUMBER                 | ISL28022                       | ISL28023                              | ISL28025                              |  |  |

|                                  | PACKAGE                     | MSOP10, QFN16                  | QFN24                                 | WLCSP-16                              |  |  |

| Temperature Rang                 | ge                          | -40°C to +125°C                | -40°C to +125°C                       | -40°C to +125°C                       |  |  |

| OV to 60V Input R                | ange                        | 0V to 60V                      | Opt 1: 0V to 60V<br>Opt 2: 0V to 16V  | Opt 1: 0V to 60V<br>Opt 2: 0V to 16V  |  |  |

| ADC                              |                             | 16-bit                         | 16-bit                                | 16-bit                                |  |  |

| +25°C Gain Error                 |                             | 0.30%                          | 0.25%                                 | 0.25%                                 |  |  |

| Current Measure I                | _SB Step                    | 10μV                           | 2.5μV                                 | 2.5μV                                 |  |  |

| +25°C Offset                     |                             | 75μV                           | 30μV                                  | 30μV                                  |  |  |

| Primary                          | Differential Shunt Input    | х                              | Х                                     | х                                     |  |  |

| Channel                          | Independent Bus Voltage     | х                              | X                                     | х                                     |  |  |

| LV Aux                           | Differential Shunt Input    |                                | Х                                     |                                       |  |  |

| Channel                          | Independent Bus Voltage     |                                | Х                                     | Х                                     |  |  |

| VBus LSB Step                    | Low Voltage Bus             |                                | 0.25mV                                | 0.25mV                                |  |  |

|                                  | High Voltage Bus            | 4mV                            | 1mV/0.25mV                            | 1mV/0.25mV                            |  |  |

| External Tempera                 | ture Sensor Input           |                                | Х                                     |                                       |  |  |

| HV Internal Regula               | ator (3.3V <sub>OUT</sub> ) |                                | X                                     | Х                                     |  |  |

| Fast OC/OV/UV AI                 | ert Outputs                 |                                | 2 Outputs                             | 2 Outputs                             |  |  |

| Margin DAC                       |                             |                                | Х                                     |                                       |  |  |

| Internal Temperat                | ure Sensor                  |                                | X                                     | Х                                     |  |  |

| User Select Conve                | rsion Mode/Sample Rate      | Х                              | X                                     | Х                                     |  |  |

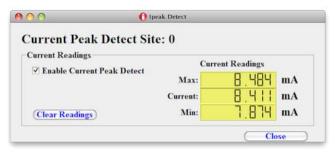

| Peak Min/Max Cu                  | rrent Registers             |                                | Х                                     | х                                     |  |  |

| Slave Address Loc                | ations                      | 16 Addresses                   | 55 Addresses                          | 55 Addresses                          |  |  |

| I <sup>2</sup> C Level Translate | ors                         |                                | Х                                     | Х                                     |  |  |

| PMBus                            |                             |                                | Х                                     | Х                                     |  |  |

| I <sup>2</sup> C/SMBus           |                             | Х                              | Х                                     | Х                                     |  |  |

| High Speed (3.4M                 | Hz) I <sup>2</sup> C Mode   | Х                              | Х                                     | Х                                     |  |  |

| External Clock Inp               | ut                          | х                              | Х                                     | Х                                     |  |  |

| Power Shutdown I                 | Mode                        | Х                              | Х                                     | X                                     |  |  |

# **Absolute Maximum Ratings**

| VCC6.0V                                                 |

|---------------------------------------------------------|

| I2CVCC Voltage                                          |

| VBUS (ISL28023FR60), VREG_IN                            |

| VBUS (ISL28023FR12)                                     |

| Common-Mode Input Voltage (VINP, VINM)                  |

| Differential Input Voltage (VINP, VINM) ±63V            |

| AUXV                                                    |

| Common-Mode Input Voltage (AUXP, AUXM)VCC - GND         |

| Differential Input Voltage (AUXP, AUXM)                 |

| Input Voltage (Digital Pins) GND - 0.3 to I2CVCC + 0.3V |

| Output Voltage (Digital Pins)GND - 0.3 to I2CVCC + 0.3V |

| Output Current (VREG_OUT, DAC_OUT)                      |

| Open-Drain Output Current                               |

| Open-Drain Voltage (SMBALERT1)24V                       |

| ESD Ratings                                             |

| Human Body Model (Tested per JESD22-A114) 6kV           |

| Machine Model (Tested per JESD22-A115)300V              |

| Charged Device Model (Tested per JESD22-C101) 2kV       |

| Latch-Up (Tested per JESD-78B) ±100mA (at +125°C)       |

# **Thermal Information**

| Thermal Resistance (Typical)                      | $\theta_{JA}$ (° C/W) | $\theta_{JC}$ (°C/W) |

|---------------------------------------------------|-----------------------|----------------------|

| 24 Ld QFN (Notes 4, 5)                            | 38                    | 2.5                  |

| Maximum Storage Temperature Range                 | 6!                    | 5°C to +150°C        |

| Maximum Junction Temperature (T <sub>JMAX</sub> ) |                       | +150°C               |

| Pb-Free Reflow Profile                            |                       | see <u>TB493</u>     |

# **Recommended Operating Conditions**

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** TA = +25 °C, I2CVCC = VCC = 3.3V, VINP = VBUS = 12V, VSENSE = VINP-VINM = 80mV, AUXP-AUXM = 80mV, AuxV = 3V, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128, unless otherwise specified. All voltages with respect to GND pin.

| PARAMETER          | DESCRIPTION                                                                 | TEST CONDITIONS                                                                | MIN<br>( <u>Note 6</u> ) | TYP      | MAX<br>(Note 6) | UNIT  |

|--------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|----------|-----------------|-------|

| PRIMARY CHANNEL    |                                                                             |                                                                                | 1                        | <b>'</b> |                 |       |

| V <sub>SHUNT</sub> | V <sub>SHUNT</sub> Measurement Range (V <sub>INP</sub> - V <sub>INM</sub> ) |                                                                                | 0                        |          | ±81.91          | mV    |

| Step_shunt         | 1LSB Step Shunt Voltage                                                     |                                                                                |                          | 2.5      |                 | μV    |

| Vshunt_vos         | V <sub>SHUNT</sub> Offset Voltage                                           |                                                                                |                          | ±2.5     | ±50             | μV    |

| Vshunt_TC          | V <sub>SHUNT</sub> Offset Voltage vs Temperature                            | T = -40°C to +125°C                                                            |                          | ±0.04    | ±0.30           | μV/°C |

| Vshunt_CMRR        | V <sub>SHUNT</sub> Vos vs Common-Mode                                       | ISL28023FR60Z<br>V <sub>BUS</sub> = 0V to 60V                                  |                          | ±0.16    | ±1.60           | μV/V  |

|                    |                                                                             | ISL28023FR12Z<br>V <sub>BUS</sub> = 0V to 16.384V                              |                          | ±0.16    | ±1.60           | μV/V  |

| Vshunt_PSRR        | V <sub>SHUNT</sub> Vos vs Power Supply                                      | V <sub>CC</sub> = ±10% of V <sub>CC</sub> nominal                              |                          | ±0.45    |                 | μV/V  |

| lvin               | V <sub>IN</sub> Input Leakage Current                                       | V <sub>IN</sub> = V <sub>SHUNT</sub> input path selected, OC detector disabled |                          | 15       | 20              | μА    |

|                    |                                                                             | V <sub>IN</sub> = V <sub>SHUNT</sub> input path selected, OC detector enabled  |                          | 30       | 40              | μА    |

|                    |                                                                             | V <sub>IN</sub> = V <sub>SHUNT</sub> input path disabled, OC detector disabled |                          | 0.05     | 0.10            | μА    |

| V <sub>BUS</sub>   | Usable Bus Voltage Measurement Range                                        | ISL28023FR60Z                                                                  | 0                        |          | 60              | ٧     |

|                    |                                                                             | ISL28023FR12Z                                                                  | 0                        |          | 16.384          | V     |

| Step_Vbus          | 1LSB Step Bus Voltage                                                       | ISL28023FR60Z                                                                  |                          | 1        |                 | mV    |

|                    |                                                                             | ISL28023FR12Z                                                                  |                          | 0.25     |                 | mV    |

Submit Document Feedback 6 Intersil\* FN8389.5 March 18, 2016

| PARAMETER       | DESCRIPTION                                               | TEST CONDITIONS                                                      | MIN<br>( <u>Note 6</u> ) | TYP   | MAX<br>(Note 6) | UNIT   |

|-----------------|-----------------------------------------------------------|----------------------------------------------------------------------|--------------------------|-------|-----------------|--------|

| Vbus_vos        | V <sub>BUS</sub> Offset Voltage                           | ISL28023FR60Z                                                        | -20                      | ±1    | 20              | m۷     |

|                 |                                                           | ISL28023FR12Z                                                        | -5                       | ± 1.5 | 5               | m۷     |

| Vbus_TC         | V <sub>BUS</sub> Offset Voltage vs Temperature            | ISL28023FR60Z; T = -40 °C to +125 °C                                 |                          | ±4    | ±100            | μV/°C  |

|                 |                                                           | ISL28023FR12Z; T = -40°C to +125°C                                   |                          | ±4    | ±100            | μV/°C  |

| Vbus_Vco        | V <sub>BUS</sub> Voltage Coefficient                      |                                                                      |                          | 50    |                 | ppm/V  |

| Vbus_PSRR       | V <sub>BUS</sub> Vos vs Power Supply                      | ISL28023FR60Z;<br>V <sub>CC</sub> = ± 10% of V <sub>CC</sub> nominal |                          | ±500  |                 | μV/V   |

|                 |                                                           | ISL28023FR12Z<br>V <sub>CC</sub> = ± 10% of V <sub>CC</sub> nominal  |                          | ±125  |                 | μV/V   |

| Zin_Vbus        | Input Impedance V <sub>BUS</sub>                          | ISL28023FR60Z                                                        |                          | 600   |                 | kΩ     |

|                 |                                                           | ISL28023FR12Z                                                        |                          | 150   |                 | kΩ     |

| AUX CHANNEL     |                                                           |                                                                      |                          |       |                 |        |

| Vshunt_aux      | V <sub>SHUNT</sub> Aux Measurement Range<br>(AuxP - AuxM) |                                                                      | 0                        |       | ±81.91          | mV     |

| Step_shunt_aux  | 1LSB Step Shunt Aux Voltage                               |                                                                      |                          | 2.5   |                 | μ۷     |

| Vshunt_aux_vos  | V <sub>SHUNT</sub> Aux Offset Voltage                     |                                                                      |                          | ±2.5  | ±50             | μ۷     |

| Vshunt_aux_TC   | V <sub>SHUNT</sub> Aux Offset Voltage vs Temperature      | T = -40°C to +125°C                                                  |                          | ±0.01 | ±0.10           | μV/°C  |

| Vshunt_aux_CMRR | V <sub>SHUNT</sub> Aux Vos vs Common-Mode                 | V <sub>BUS</sub> = 0V to VCC                                         |                          | ±0.1  | ±4              | μV/V   |

| Vshunt_aux_PSRR | V <sub>SHUNT</sub> Aux Vos vs Power Supply                | V <sub>CC</sub> = ± 10% of V <sub>CC</sub> nominal                   |                          | ±0.45 |                 | μV/V   |

| Zin_aux_in      | AUX Input Impedance                                       | Aux = AUXVshunt input path selected                                  |                          | 1     |                 | МΩ     |

|                 |                                                           | Aux = AUXVshunt input path disabled                                  |                          | 10    |                 | MΩ     |

| Vauxv           | Usable AVXV Voltage Measurement Range                     |                                                                      | 0                        |       | vcc             | V      |

| Step_auxv       | 1LSB Step AUXV Voltage                                    |                                                                      |                          | 100   |                 | μ۷     |

| Vauxv_vos       | Vauxv Offset Voltage                                      |                                                                      |                          | ±0.3  | ±4              | m۷     |

| Vauxv_TC        | Vauxv Offset Voltage vs Temperature                       | T = -40°C to +125°C                                                  |                          | ±0.2  | ±22             | μV/°C  |

| Vauxv_PSRR      | Vauxv Vos vs Power Supply                                 | V <sub>CC</sub> = ±10% of V <sub>CC</sub> nominal                    |                          | ±1    |                 | mV/V   |

| Zin_auxv        | Auxv Input Impedance                                      | Input path selected                                                  |                          | 200   |                 | kΩ     |

|                 |                                                           | Input path disabled                                                  |                          | 10    |                 | МΩ     |

| ADC PARAMETERS  |                                                           |                                                                      |                          |       |                 |        |

|                 | ADC Resolution                                            |                                                                      |                          | 16    |                 | Bits   |

|                 | Primary Shunt Voltage Gain Error                          |                                                                      |                          | ±0.05 | ±0.25           | %      |

|                 |                                                           | T = -40°C to +125°C                                                  |                          |       | ±60             | ppm/°0 |

|                 | Primary Bus Voltage Gain Error                            |                                                                      |                          | ±0.05 | ±0.2            | %      |

|                 |                                                           | T = -40°C to +125°C                                                  |                          | 10    | ±70             | ppm/°0 |

|                 | Aux Shunt Voltage Gain Error                              |                                                                      |                          | ±0.02 | ±0.25           | %      |

|                 |                                                           | T = -40°C to +125°C                                                  |                          |       | ±65             | ppm/°0 |

|                 | Aux Bus Voltage Gain Error                                |                                                                      |                          | ±0.02 | ±0.2            | %      |

|                 |                                                           | T = -40°C to +125°C                                                  |                          |       | ±65             | ppm/°( |

|                 | Differential Nonlinearity                                 |                                                                      |                          | ±1    |                 | LSB    |

| PARAMETER               | DESCRIPTION                                                    | TEST CONDITIONS                     | MIN<br>(Note 6)                                                                                                                                                                                                                                                                                         | TYP   | MAX<br>(Note 6) | UNIT    |

|-------------------------|----------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|---------|

| ADC TIMING              | 223 11910                                                      | 1.2.1 33.1.31.1010                  | (                                                                                                                                                                                                                                                                                                       | 1     | (               |         |

| t <sub>s Power-up</sub> | ADC Conversion Time Resolution                                 | ADC[2:0] = 0h                       |                                                                                                                                                                                                                                                                                                         | 64    | 70.4            | μs      |

| 'S Fower-up             | ,                                                              | ADC[2:0] = 1h                       |                                                                                                                                                                                                                                                                                                         |       | 140.8           | μs      |

|                         |                                                                | ADC[2:0] = 2h                       |                                                                                                                                                                                                                                                                                                         |       | 281.6           | μs      |

|                         |                                                                | ADC[2:0] = 3h                       |                                                                                                                                                                                                                                                                                                         |       | 563.2           | μs      |

|                         |                                                                | ADC[2:0] = 4, 5h                    | TEST CONDITIONS  (Note 6)  TYP  (Note 6)  100  101  128  140  128  140  128  140  128  140  128  140  129  140  141  142  140  140  140  141  141 | 1.126 | ms              |         |

|                         |                                                                | ADC[2:0] = 6, 7h                    |                                                                                                                                                                                                                                                                                                         |       | 2.253           | ms      |

| HRESHOLD DETEC          | TORS                                                           | 7.50[-10] 0, 111                    |                                                                                                                                                                                                                                                                                                         |       |                 |         |

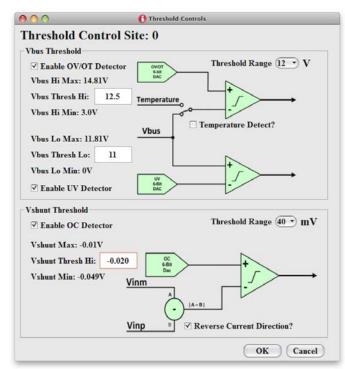

|                         | Overvoltage (OV) V <sub>BUS</sub> Threshold Voltage<br>Range   | Vbus_Thres_Rng[2:0] = ALL           | 25                                                                                                                                                                                                                                                                                                      |       | 125             | % of FS |

|                         | Overvoltage (OV) V <sub>BUS</sub> Threshold DAC Step<br>Size   | Vbus_Thres_Rng[2:0] = ALL           |                                                                                                                                                                                                                                                                                                         | 1.56  |                 | % of FS |

|                         | Undervoltage (UV) V <sub>BUS</sub> Threshold Voltage<br>Range  | Vbus_Thres_Rng[2:0] = ALL           | 0                                                                                                                                                                                                                                                                                                       |       | 100             | % of FS |

|                         | Undervoltage (UV) V <sub>BUS</sub> Threshold DAC<br>Step Size  | Vbus_Thres_Rng[2:0] = ALL           |                                                                                                                                                                                                                                                                                                         | 1.56  |                 | % of FS |

|                         | V <sub>BUS</sub> Threshold Detector Full-Scale                 | Vbus_Thres_Rng[2:0] = 0; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 48    |                 | V       |

|                         | Settings<br>ISL28025FI60Z                                      | Vbus_Thres_Rng[2:0] = 1; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 24    |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 2; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 12    |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 3; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 5     |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 4; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 3.3   |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 5; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 2.5   |                 | ٧       |

|                         | V <sub>BUS</sub> Threshold Detector Full-Scale                 | Vbus_Thres_Rng[2:0] = 0; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 12    |                 | V       |

|                         | Settings<br>ISL28025FI12Z                                      | Vbus_Thres_Rng[2:0] = 1; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 6     |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 2; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 3     |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 3; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 2.5   |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 4; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 0.825 |                 | V       |

|                         |                                                                | Vbus_Thres_Rng[2:0] = 5; OT_SEL = 0 |                                                                                                                                                                                                                                                                                                         | 0.625 |                 | V       |

|                         | Over-Temperature Threshold Detector<br>Range                   | OT_SEL = 1                          | -40                                                                                                                                                                                                                                                                                                     |       | 135             | °C      |

|                         | Over-Temperature Threshold Detector<br>Resolution Error        |                                     |                                                                                                                                                                                                                                                                                                         | ±5    |                 | °C      |

|                         | Overcurrent (OC) V <sub>SHUNT</sub> Threshold<br>Voltage Range | OCRNG = ALL                         | 25                                                                                                                                                                                                                                                                                                      |       | 125             | % of FS |

|                         | Overcurrent (OC) V <sub>SHUNT</sub> Threshold DAC<br>Step Size | OCRNG = ALL                         |                                                                                                                                                                                                                                                                                                         | 1.56  |                 | % of FS |

|                         | V <sub>SHUNT</sub> Threshold Detector Full-Scale<br>Settings   | OCRNG = 0                           |                                                                                                                                                                                                                                                                                                         | 80    |                 | mV      |

|                         | oottings                                                       | OCRNG = 1                           |                                                                                                                                                                                                                                                                                                         | 40    |                 | mV      |

| IARGINING DAC, A        | NALOG OUTPUT                                                   | T                                   |                                                                                                                                                                                                                                                                                                         | 1     |                 | Т       |

|                         | Resolution                                                     |                                     |                                                                                                                                                                                                                                                                                                         | 8     |                 | Bits    |

|                         | DNL                                                            |                                     |                                                                                                                                                                                                                                                                                                         | ±1    |                 | LSB     |

| PARAMETER                     | DESCRIPTION                                      | TEST CONDITIONS                    | MIN<br>( <u>Note 6</u> ) | ТҮР              | MAX<br>(Note 6) | UNIT |

|-------------------------------|--------------------------------------------------|------------------------------------|--------------------------|------------------|-----------------|------|

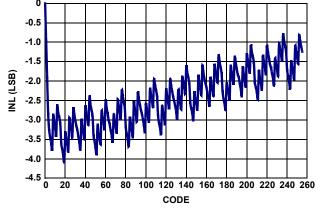

|                               | INL                                              | MDAC[7:0] = 0 to 256               |                          | ±3               |                 | LSB  |

|                               | Gain Error                                       | DAC_MS[2:0] = 0                    |                          | ±2.5             |                 | %    |

|                               | Offset Error                                     | DAC_MS[2:0] = 0                    |                          | ±2               |                 | m۷   |

|                               | Output Voltage                                   |                                    | 0.055                    |                  | 2*Vms           | V    |

| VMS                           | DAC Mid-Scale                                    | DAC_MS[2:0] = 0                    |                          | 0.4              |                 | ٧    |

|                               |                                                  | DAC_MS[2:0] = 1                    |                          | 0.5              |                 | V    |

|                               |                                                  | DAC_MS[2:0] = 2                    |                          | 0.6              |                 | V    |

|                               |                                                  | DAC_MS[2:0] = 3                    |                          | 0.7              |                 | ٧    |

|                               |                                                  | DAC_MS[2:0] = 4                    |                          | 0.8              |                 | V    |

|                               |                                                  | DAC_MS[2:0] = 5                    |                          | 0.9              |                 | ٧    |

|                               |                                                  | DAC_MS[2:0] = 6                    |                          | 1.0              |                 | ٧    |

|                               |                                                  | DAC_MS[2:0] = 7                    |                          | 1.2              |                 | ٧    |

|                               | Slew Rate                                        |                                    |                          | 1                |                 | V/µs |

|                               | Output Current                                   |                                    |                          | 1                |                 | mA   |

|                               | Short-Circuit Current                            | DAC_OUT = V <sub>CC</sub>          |                          |                  | 17              | mA   |

|                               |                                                  | DAC_OUT = GND                      |                          |                  | 4.2             | mA   |

|                               | Start-Up Time                                    |                                    |                          | 100              |                 | μs   |

| OLTAGE REGULATO               | R SPECIFICATION                                  |                                    |                          |                  | I .             |      |

|                               | Input Voltage at REG_IN                          |                                    | 4.5                      |                  | 60              | ٧    |

|                               | Output Regulation Voltage                        |                                    | 3.18                     | 3.30             | 3.35            | V    |

|                               | Line Regulation                                  | V <sub>IN</sub> = 4.5V to 60V      |                          | 53               | 150             | μV/V |

|                               | Load Regulation                                  | I <sub>LOAD</sub> = 3.3mA to 6mA   |                          | 0.2              | 1.4             | mV/m |

|                               | Capacitance Drive                                |                                    | 0.01                     |                  | 10              | μF   |

|                               | Output Short-Circuit                             | T = -40°C to +125°C                |                          | 10               |                 | mA   |

|                               | Max Load Current                                 | T = -40°C to +125°C                |                          | 6                |                 | mA   |

|                               | Start-Up Time                                    |                                    |                          | 1                |                 | ms   |

| EMPERATURE SEN                | SOR                                              |                                    |                          |                  |                 | 1    |

|                               | Temperature Sensor Measurement Range             |                                    | -40                      |                  | 125             | °C   |

|                               | Temperature Accuracy                             | T = +25°C                          |                          | +1               |                 | °C   |

|                               | Temperature Resolution                           |                                    |                          | 0.5              |                 | °C   |

|                               | Measurement Time                                 |                                    |                          | 0.5              |                 | ms   |

| MBus/I <sup>2</sup> C INTERFA | ACE SPECIFICATIONS                               |                                    |                          |                  |                 |      |

| V <sub>IL</sub>               | SMBDAT and SMBCLK Input Buffer LOW Voltage       |                                    | -0.3                     |                  | 0.3 x<br>I2CVCC | V    |

| V <sub>IH</sub>               | SMBDAT and SMBCLK Input Buffer HIGH Voltage      |                                    | 0.7 x I2CVCC             |                  | 12CVCC +<br>0.3 | V    |

| Hysteresis                    | SMBDAT and SMBCLK Input Buffer<br>Hysteresis     |                                    |                          | 0.05 x<br>I2CVCC |                 | V    |

| V <sub>OL</sub>               | SMBDAT Output Buffer LOW Voltage,<br>Sinking 3mA | I2CVCC = 5V, I <sub>OL</sub> = 3mA | 0                        | 0.02             | 0.4             | V    |

| PARAMETER           | DESCRIPTION                                                      | TEST CONDITIONS                                                                                                                                         | MIN<br>( <u>Note 6</u> ) | TYP | MAX<br>( <u>Note 6</u> ) | UNI |

|---------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|-----|

| C <sub>PIN</sub>    | SMBDAT and SMBCLK Pin Capacitance                                | $T_A = +25$ °C, $f = 1$ MHz, $I2CVCC = 5V$ , $V_{IN} = 0V$ , $V_{OUT} = 0V$                                                                             |                          |     | 10                       | pF  |

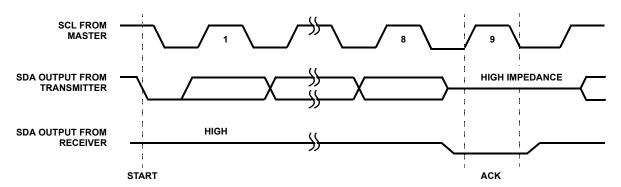

| fSMBCLK             | SMBCLK Frequency                                                 |                                                                                                                                                         |                          |     | 400                      | kH  |

| t <sub>IN</sub>     | Pulse Width Suppression Time at SMBDAT and SMBCLK Inputs         | Any pulse narrower than the max spec is suppressed                                                                                                      |                          |     | 50                       | ns  |

| t <sub>AA</sub>     | SMBCLK Falling Edge to SMBDAT Output<br>Data Valid               | SMBCLK falling edge crossing 30% of I2CVCC, until SMBDAT exits the 30% to 70% of I <sup>2</sup> CVCC window                                             |                          |     | 900                      | ns  |

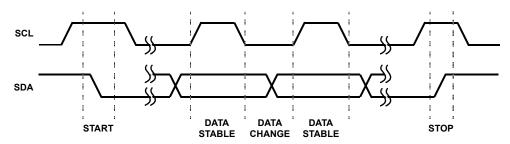

| <sup>t</sup> BUF    | Time the Bus Must be Free Before the Start of a New Transmission | SMBDAT crossing 70% of I2CVCC during a STOP condition, to SMBDAT crossing 70% of I2CVCC during the following START condition                            | 1300                     |     |                          | ns  |

| t <sub>LOW</sub>    | Clock LOW Time                                                   | Measured at the 30% of I2CVCC crossing                                                                                                                  | 1300                     |     |                          | ns  |

| tHIGH               | Clock HIGH Time                                                  | Measured at the 70% of I2CVCC crossing                                                                                                                  | 600                      |     |                          | ns  |

| <sup>t</sup> SU:STA | START Condition Setup Time                                       | SMBCLK rising edge to SMBDAT falling edge. Both crossing 70% of I2CVCC                                                                                  | 600                      |     |                          | ns  |

| <sup>t</sup> hd:STA | START Condition Hold Time                                        | From SMBDAT falling edge crossing 30% of I2CVCC to SMBCLK falling edge crossing 70% of I2CVCC                                                           | 600                      |     |                          | ns  |

| <sup>t</sup> SU:DAT | Input Data Setup Time                                            | From SMBDAT exiting the 30% to 70% of V <sub>CC</sub> window, to SMBCLK rising edge crossing 30% of I2CVCC                                              | 100                      |     |                          | ns  |

| t <sub>HD:DAT</sub> | Input Data Hold Time                                             | From SMBCLK falling edge crossing 30% of I2CVCC to SMBDAT entering the 30% to 70% of I2CVCC window                                                      | 20                       |     | 900                      | ns  |

| t <sub>SU:STO</sub> | STOP Condition Setup Time                                        | From SMBCLK rising edge crossing 70% of I2CVCC, to SMBDAT rising edge crossing 30% of I2CVCC                                                            | 600                      |     |                          | ns  |

| t <sub>HD:STO</sub> | STOP Condition Hold Time                                         | From SMBDAT rising edge to SMBCLK falling edge. Both crossing 70% of I2CVCC                                                                             | 600                      |     |                          | ns  |

| t <sub>DH</sub>     | Output Data Hold Time                                            | From SMBCLK falling edge crossing 30% of I2CVCC, until SMBDAT enters the 30% to 70% of I2CVCC window                                                    | 0                        |     |                          | ns  |

| t <sub>R</sub>      | SMBDAT and SMBCLK Rise Time                                      | From 30% to 70% of I2CVCC                                                                                                                               | 20 + 0.1 x Cb            |     | 300                      | ns  |

| t <sub>F</sub>      | SMBDAT and SMBCLK Fall Time                                      | From 70% to 30% of I2CVCC                                                                                                                               | 20 + 0.1 x Cb            |     | 300                      | ns  |

| Cb                  | Capacitive Loading of SMBDAT or SMBCLK                           | Total on-chip and off-chip                                                                                                                              | 10                       |     | 400                      | pl  |

| R <sub>PU</sub>     | SMBDAT and SMBCLK Bus Pull-up Resistor Off-chip                  | Maximum is determined by $t_R$ and $t_F$ For Cb = 400pF, max is about $2k\Omega \sim 2.5k\Omega$ For Cb = 40pF, max is about $15k\Omega \sim 20k\Omega$ | 1                        |     |                          | kΩ  |

| WER SUPPLY          |                                                                  |                                                                                                                                                         | - 1                      |     |                          |     |

| Vvcc                | Power Supply Voltage at V <sub>CC</sub>                          |                                                                                                                                                         | 3.0                      | 3.3 | 5.5                      | ٧   |

| Vi2cvcc             | Power Supply Voltage at I <sup>2</sup> CVCC                      | f = DC to 400kHz                                                                                                                                        | 1.2                      | 3.3 | 5.5                      | ٧   |

|                     | Only ADC in Conversion Mode                                      | All other blocks are disabled                                                                                                                           |                          | 690 | 830                      | μA  |

**Electrical Specifications** TA = +25°C, I2CVCC = VCC = 3.3V, VINP = VBUS = 12V, VSENSE = VINP-VINM = 80mV, AUXP-AUXM = 80mV, AuxV = 3V, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128, unless otherwise specified. All voltages with respect to GND

| PARAMETER  | DESCRIPTION                          | TEST CONDITIONS                     | MIN<br>( <u>Note 6</u> ) | TYP  | MAX<br>(Note 6) | UNIT |

|------------|--------------------------------------|-------------------------------------|--------------------------|------|-----------------|------|

|            | Only ADC in Idle Mode                | All other blocks are disabled       |                          | 640  | 705             | μΑ   |

|            | Only Threshold Detectors             | All three detectors are active      |                          | 760  | 945             | μΑ   |

|            | Only Margin DAC                      | All other blocks are disabled       |                          | 240  | 286             | μΑ   |

|            | Fully Enabled Chip Current           | All functional blocks enabled       |                          | 1240 | 1545            | μΑ   |

|            | Fully Disabled Chip Current          | All functional blocks disabled      |                          | 5    | 15              | μΑ   |

| lvreg_in   | Voltage Regulator                    | Vreg_in = 4.5V to 60V; Rload = open |                          | 26   | 35              | μΑ   |

| li2cvcc    | I <sup>2</sup> C Supply Current      | SMBCLK = 100kHz; I2CVCC = 3.3V      |                          | 15   |                 | μΑ   |

| li2cvcc_pd | I <sup>2</sup> C Idle Supply Current | Input signals are static            |                          | 100  |                 | nA   |

#### NOTE:

intersil Submit Document Feedback 11

<sup>6.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Compliance to datasheet limits is assured by one or more of the following methods: production test, characterization and design.

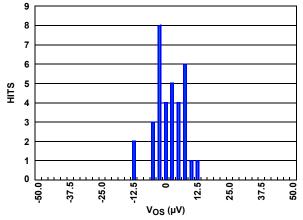

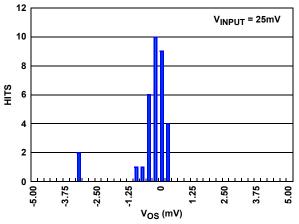

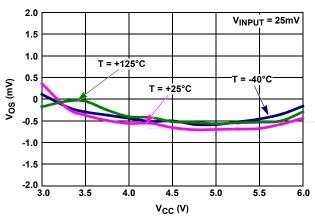

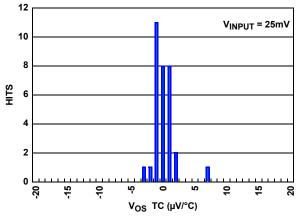

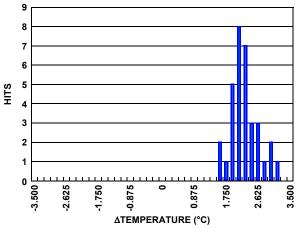

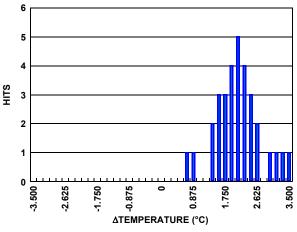

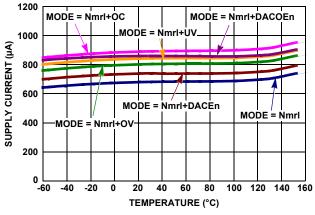

# Typical Performance Curves TA = +25°C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified.

FIGURE 3. PRIMARY V<sub>SHUNT</sub> V<sub>OS</sub>

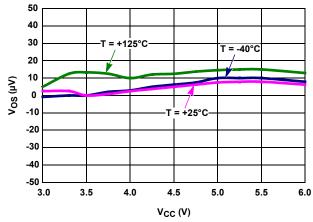

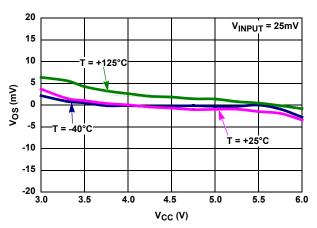

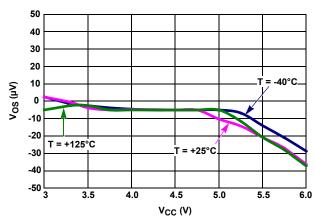

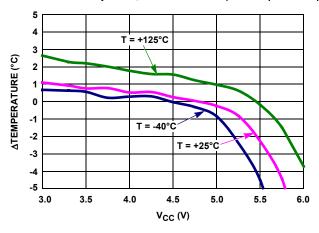

FIGURE 4. PRIMARY V<sub>SHUNT</sub> V<sub>OS</sub> vs VCC

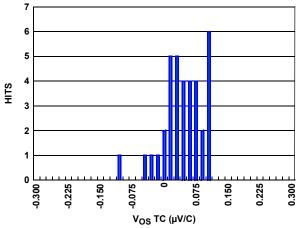

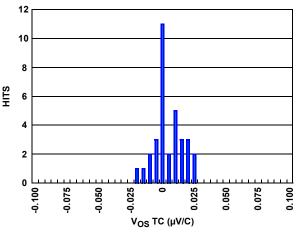

FIGURE 5. PRIMARY  $V_{SHUNT} V_{OS}$  TC (-40 °C TO +125 °C)

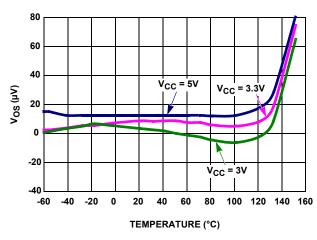

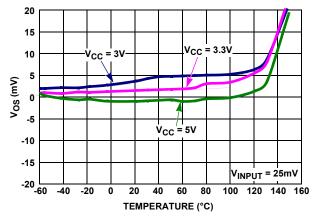

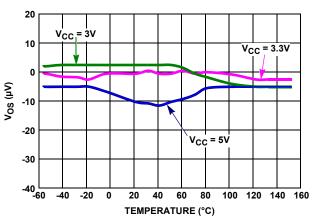

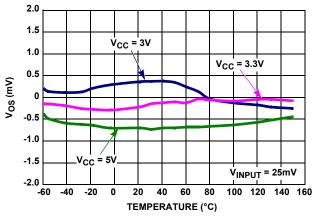

FIGURE 6. PRIMARY V<sub>SHUNT</sub> VOS vs TEMPERATURE

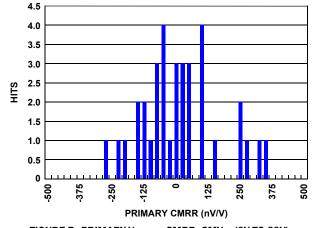

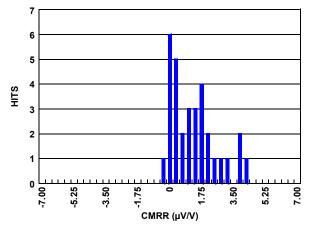

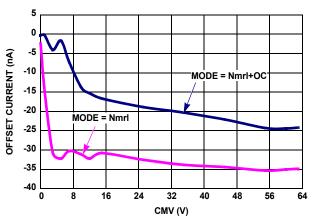

FIGURE 7. PRIMARY  $V_{SHUNT}$  CMRR, CMV = (0V TO 60V)

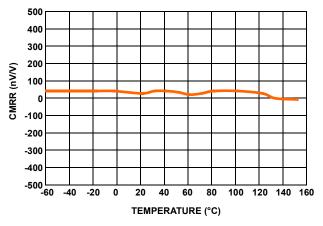

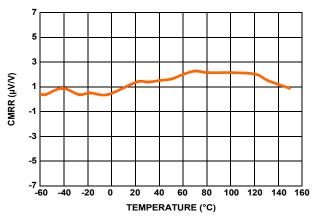

FIGURE 8. PRIMARY V<sub>SHUNT</sub> CMRR vs TEMPERATURE (CMV = 0V TO 60V)

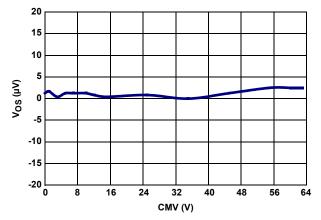

FIGURE 9. PRIMARY V<sub>SHUNT</sub> CMRR vs CMV

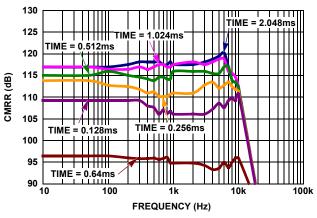

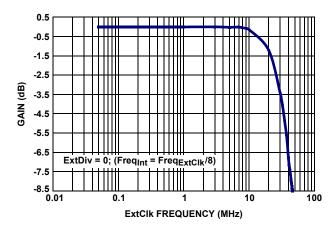

FIGURE 10. PRIMARY V<sub>SHUNT</sub> AC CMRR vs FREQUENCY

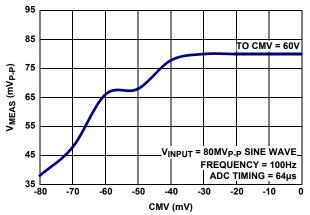

FIGURE 11. PRIMARY V<sub>SHUNT</sub> COMMON-MODE RANGE

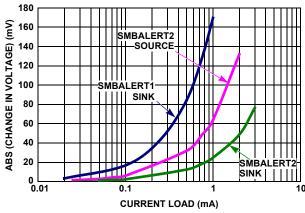

FIGURE 12. SMBALERT CURRENT DRIVES

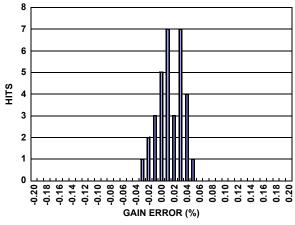

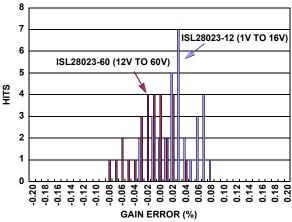

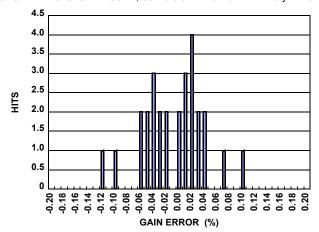

FIGURE 13. PRIMARY V<sub>SHUNT</sub> ADC GAIN ERROR

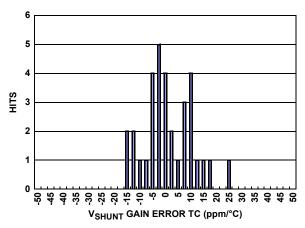

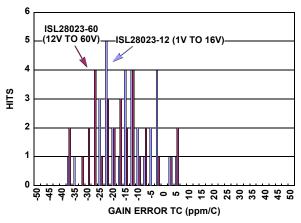

FIGURE 14. PRIMARY V<sub>SHUNT</sub> ADC GAIN ERROR TC

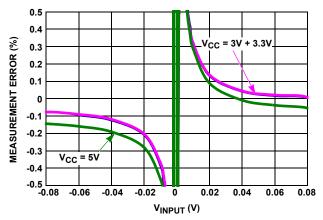

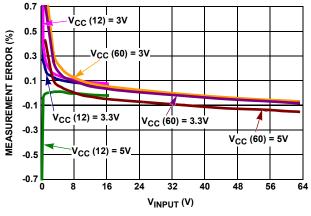

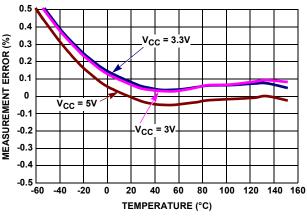

FIGURE 15. PRIMARY V<sub>SHUNT</sub> MEASUREMENT ERROR vs INPUT

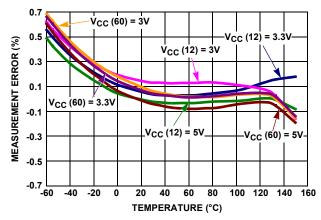

FIGURE 16. PRIMARY V<sub>SHUNT</sub> MEASUREMENT ERROR vs TEMPERATURE

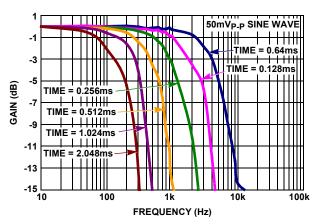

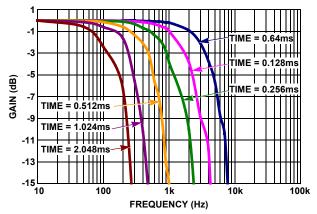

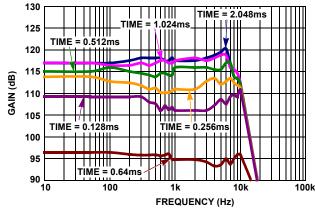

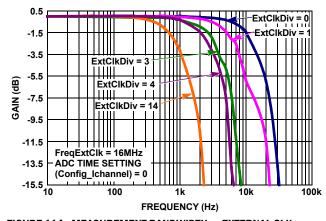

FIGURE 17. PRIMARY V<sub>SHUNT</sub> BANDWIDTH vs ADC TIMING

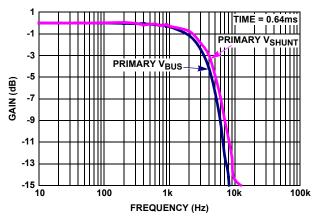

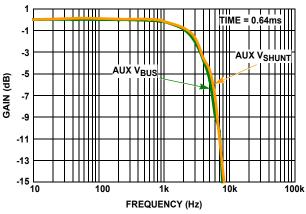

FIGURE 18. PRIMARY  $V_{SHUNT}$  and  $V_{BUS}$  vs frequency

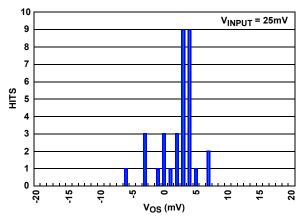

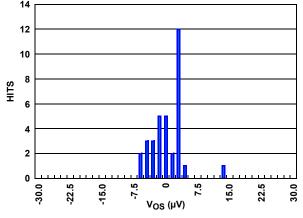

FIGURE 19. PRIMARY V<sub>BUS</sub> V<sub>OS</sub>

FIGURE 20. PRIMARY  $V_{BUS} \ V_{OS} \ vs \ V_{CC}$

# Typical Performance Curves $T_A = +25$ °C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified. (Continued)

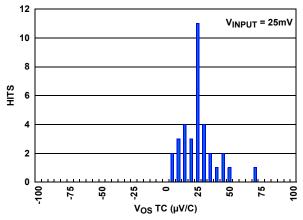

FIGURE 21. PRIMARY V<sub>BUS</sub> V<sub>OS</sub> TC

FIGURE 22. PRIMARY V<sub>BUS</sub> V<sub>OS</sub> vs TEMPERATURE

FIGURE 23. PRIMARY V<sub>BUS</sub> ADC GAIN ERROR

FIGURE 24. PRIMARY V<sub>BUS</sub> ADC GAIN ERROR TC

FIGURE 25. PRIMARY  $V_{\mbox{\scriptsize BUS}}$  MEASUREMENT ERROR vs INPUT

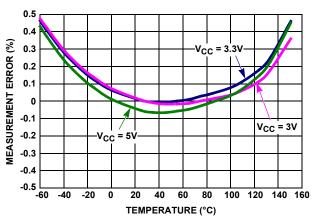

FIGURE 26. PRIMARY  $V_{\mbox{\scriptsize BUS}}$  MEASUREMENT ERROR vs TEMPERATURE

#

FIGURE 27. AUXILIARY V<sub>SHUNT</sub> V<sub>OS</sub>

FIGURE 28. AUXILIARY  $V_{SHUNT}\,V_{OS}\,vs\,V_{CC}$

FIGURE 29. AUXILIARY V<sub>SHUNT</sub> V<sub>OS</sub> TC (-40 °C TO +125 °C)

FIGURE 30. AUXILIARY V<sub>SHUNT</sub> V<sub>OS</sub> vs TEMPERATURE

FIGURE 31. AUXILIARY V<sub>SHUNT</sub> CMRR, CMV = (0V TO 3.3V)

FIGURE 32. AUXILIARY V<sub>SHUNT</sub> CMRR vs TEMPERATURE (CMV = 0V TO 3.3V)

# Typical Performance Curves TA = +25°C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified. (Continued)

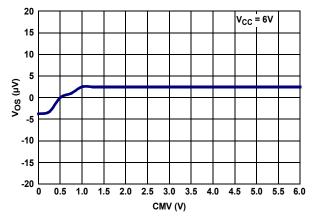

FIGURE 33. AUXILIARY V<sub>SHUNT</sub> V<sub>OS</sub> vs CMV

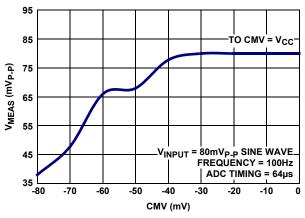

FIGURE 34. AUXILIARY V<sub>SHUNT</sub> COMMON-MODE RANGE

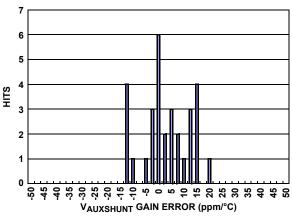

FIGURE 35. AUXILIARY V<sub>SHUNT</sub> ADC GAIN ERROR

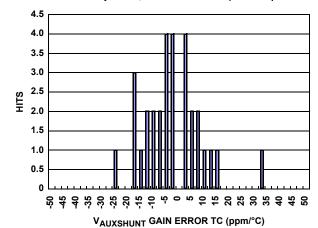

FIGURE 36. AUXILIARY V<sub>SHUNT</sub> ADC GAIN ERROR TC

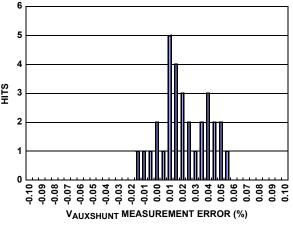

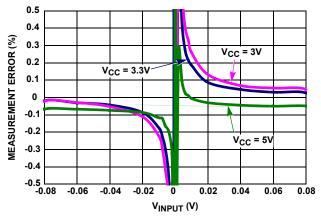

FIGURE 37. AUXILIARY  $V_{SHUNT}$  MEASUREMENT ERROR vs INPUT

FIGURE 38. AUXILIARY V<sub>SHUNT</sub> MEASUREMENT ERROR vs TEMPERATURE

FIGURE 39. AUXILIARY  $V_{\mbox{\footnotesize{BUS}}}$  BANDWIDTH vs ADC TIMING

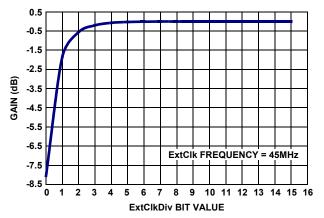

FIGURE 40. AUXILIARY V<sub>SHUNT</sub> AND V<sub>BUS</sub> vs FREQUENCY

FIGURE 41. AUXILIARY VBUS VOS

FIGURE 42. AUXILIARY VBUS VOS VS VCC

FIGURE 43. AUXILIARY V<sub>BUS</sub> V<sub>OS</sub> TC

FIGURE 44. AUXILIARY V<sub>BUS</sub> VOS vs TEMPERATURE

# Typical Performance Curves $T_A = +25$ °C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified. (Continued)

FIGURE 45. AUXILIARY V<sub>BUS</sub> ADC GAIN ERROR

FIGURE 46. AUXILIARY V<sub>BUS</sub> ADC GAIN ERROR TC

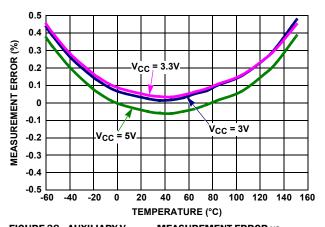

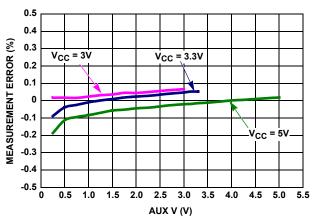

FIGURE 47. AUXILIARY V<sub>BUS</sub> MEASUREMENT ERROR vs INPUT

FIGURE 48. AUXILIARY V<sub>BUS</sub> MEASUREMENT ERROR vs TEMPERATURE

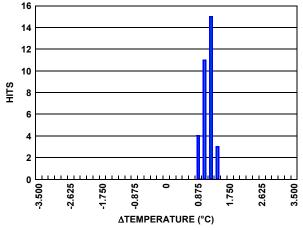

FIGURE 49. INTERNAL TEMPERATURE ACCURACY AT T = +25°C

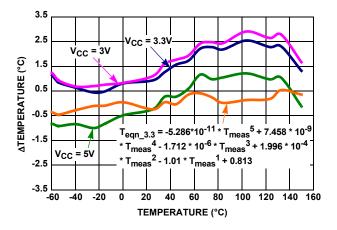

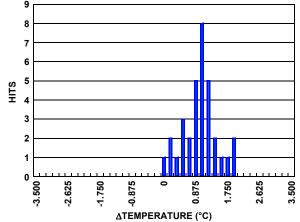

FIGURE 50. INTERNAL TEMPERATURE SENSOR ACCURACY

FIGURE 51. INTERNAL TEMPERATURE ACCURACY AT T = -40°C

FIGURE 52. INTERNAL TEMPERATURE ACCURACY vs V<sub>CC</sub>

FIGURE 53. INTERNAL TEMPERATURE ACCURACY AT T = +85°C

FIGURE 54. INTERNAL TEMPERATURE ACCURACY AT T = +125°C

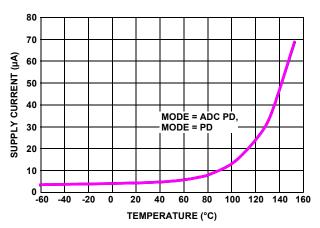

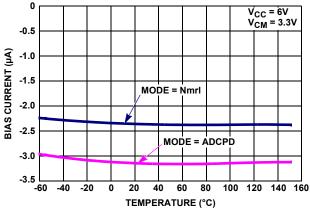

FIGURE 55. SUPPLY CURRENT vs TEMPERATURE

FIGURE 56. POWER-DOWN SUPPLY CURRENT vs TEMPERATURE

Submit Document Feedback 20 FN8389.5 intersil March 18, 2016

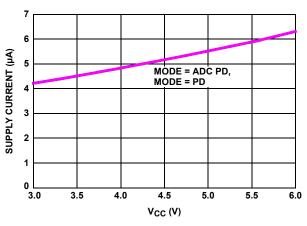

FIGURE 57. SUPPLY CURRENT vs SUPPLY VOLTAGE

FIGURE 58. SUPPLY CURRENT vs SUPPLY VOLTAGE (POWER-DOWN MODES)

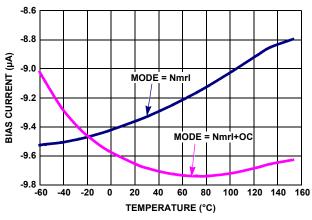

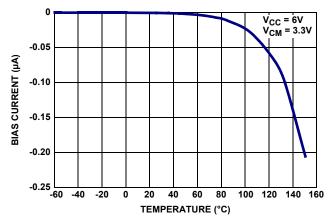

FIGURE 59. PRIMARY  $V_{\mbox{\scriptsize SHUNT}}$  BIAS CURRENT vs TEMPERATURE

FIGURE 60. PRIMARY V<sub>SHUNT</sub> BIAS CURRENT vs TEMPERATURE (POWER-DOWN MODE)

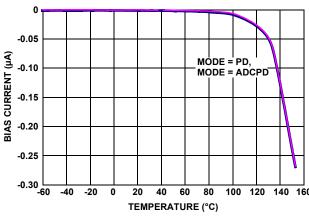

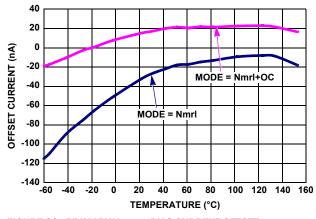

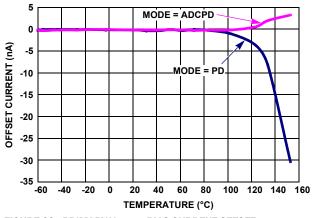

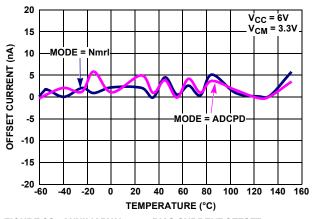

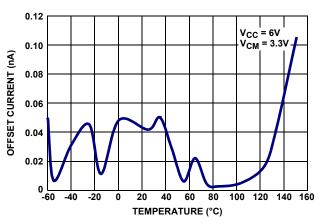

FIGURE 61. PRIMARY V<sub>SHUNT</sub> BIAS CURRENT OFFSET vs **TEMPERATURE**

FIGURE 62. PRIMARY V<sub>SHUNT</sub> BIAS CURRENT OFFSET vs TEMPERATURE (POWER-DOWN MODE)

Submit Document Feedback 21 FN8389.5 intersil March 18, 2016

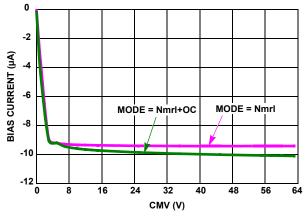

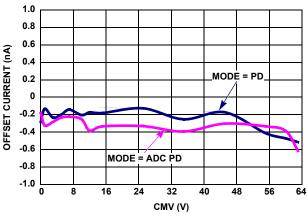

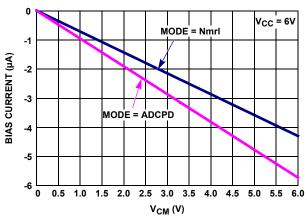

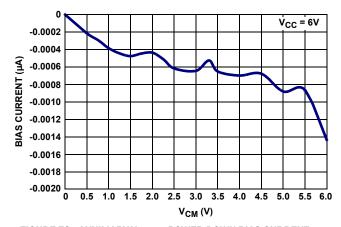

FIGURE 63. PRIMARY V<sub>SHUNT</sub> BIAS CURRENT vs COMMON-MODE VOLTAGE

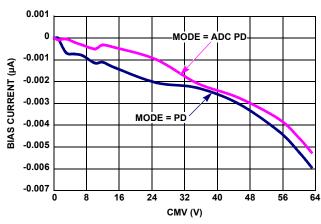

FIGURE 64. PRIMARY V<sub>SHUNT</sub> BIAS CURRENT vs COMMON-MODE **VOLTAGE (POWER-DOWN MODES)**

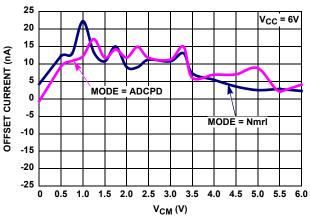

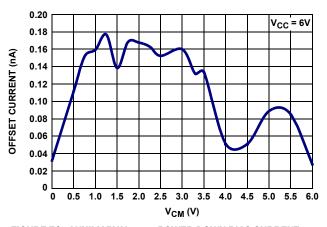

FIGURE 65. PRIMARY V<sub>SHUNT</sub> OFFSET CURRENT vs COMMON-MODE

FIGURE 66. PRIMARY V<sub>SHUNT</sub> OFFSET CURRENT vs COMMON-MODE VOLTAGE (POWER-DOWN MODES)

FIGURE 67. AUXILIARY V<sub>SHUNT</sub> BIAS CURRENT vs TEMPERATURE

FIGURE 68. AUXILIARY V<sub>SHUNT</sub> BIAS CURRENT OFFSET vs **TEMPERATURE**

Submit Document Feedback FN8389.5 22 intersil March 18, 2016

# Typical Performance Curves TA = +25°C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified. (Continued)

FIGURE 69. AUXILIARY V<sub>SHUNT</sub> POWER-DOWN BIAS CURRENT vs TEMPERATURE

FIGURE 70. AUXILIARY V<sub>SHUNT</sub> POWER-DOWN BIAS CURRENT OFFSET vs TEMPERATURE

FIGURE 71. AUXILIARY V<sub>SHUNT</sub> BIAS CURRENT vs COMMON-MODE

FIGURE 72. AUXILIARY V<sub>SHUNT</sub> BIAS CURRENT OFFSET vs COMMON-MODE VOLTAGE

FIGURE 73. AUXILIARY V<sub>SHUNT</sub> POWER-DOWN BIAS CURRENT vs COMMON-MODE VOLTAGE

FIGURE 74. AUXILIARY V<sub>SHUNT</sub> POWER-DOWN BIAS CURRENT OFFSET vs COMMON-MODE VOLTAGE

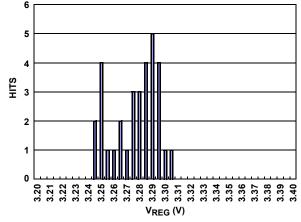

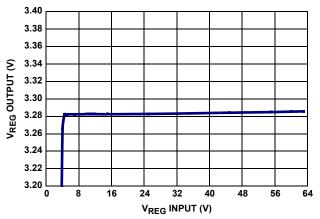

FIGURE 75. V<sub>REG</sub> OUTPUT VOLTAGE DISTRIBUTION

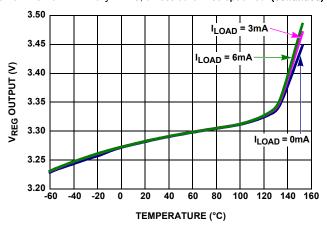

FIGURE 76. V<sub>REG</sub> OUTPUT vs TEMPERATURE

FIGURE 77. V<sub>REG</sub> OUTPUT vs INPUT VOLTAGE

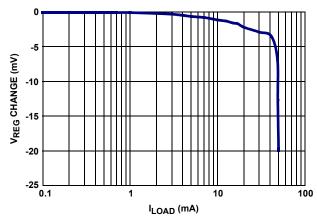

FIGURE 78. V<sub>REG</sub> OUTPUT vs CURRENT LOAD

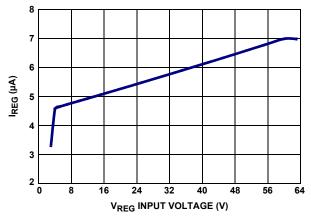

FIGURE 79. V<sub>REG</sub> INPUT CURRENT vs INPUT VOLTAGE

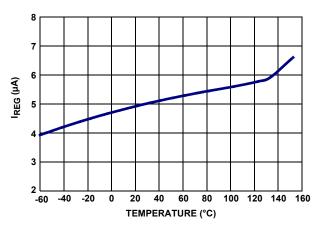

FIGURE 80. V<sub>REG</sub> INPUT CURRENT vs TEMPERATURE

Submit Document Feedback 24 intersil FN8389.5 March 18, 2016

#

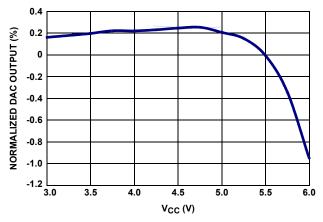

FIGURE 81. MARGIN DAC vs V<sub>CC</sub>

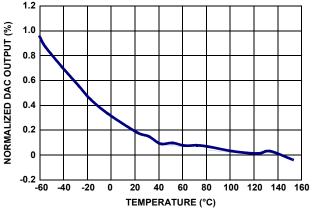

FIGURE 82. NORMALIZED DAC OUTPUT vs TEMPERATURE

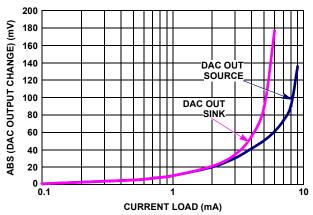

FIGURE 83. MARGIN DAC vs CURRENT LOAD

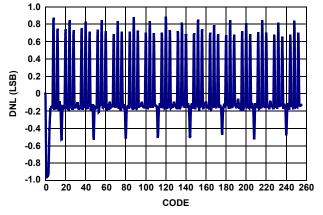

FIGURE 84. MARGIN DAC DNL

FIGURE 85. MARGIN DAC INL PER CODE

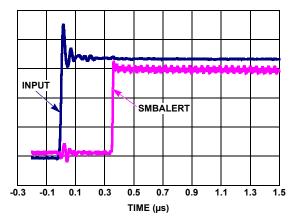

FIGURE 86. OV OR UV OR OC ALERT RESPONSE TIME

Submit Document Feedback 25 intersil FN8389.5 March 18, 2016

# Typical Performance Curves TA = +25°C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified. (Continued)

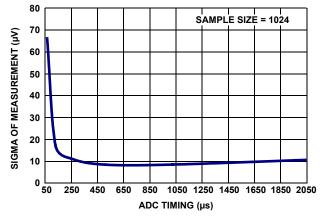

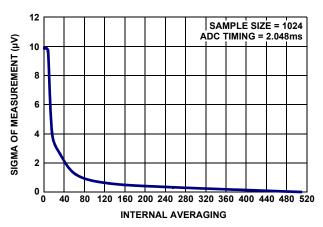

FIGURE 87. PRIMARY SHUNT STABILITY: STDEV vs ACQUISITION TIME

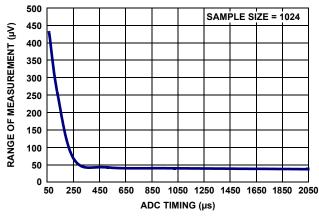

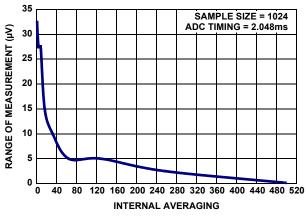

FIGURE 88. PRIMARY SHUNT STABILITY: RANGE vs ACQUISITION TIME

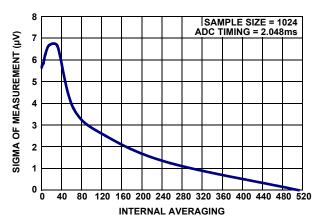

FIGURE 89. PRIMARY SHUNT STABILITY: STDEV vs INTERNAL **AVERAGING**

FIGURE 90. PRIMARY SHUNT STABILITY: RANGE vs INTERNAL **AVERAGING**

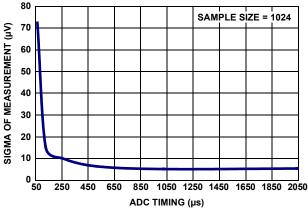

FIGURE 91. AUXILIARY SHUNT STABILITY: STDEV vs ACQUISITION TIME

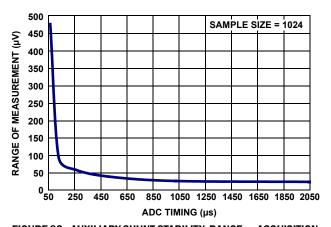

FIGURE 92. AUXILIARY SHUNT STABILITY: RANGE vs ACQUISITION

Submit Document Feedback intersil FN8389.5 26 March 18, 2016

# Typical Performance Curves TA = +25°C, VCC = 3.3V, VINP = VBUS = 12V, AUXP = AUXV = 3V,

VSHUNT = VAUXSHUNT = 80mV, Conversion Time: Aux = Primary = 2.05ms, Internal AVG Aux = Primary = 128; unless otherwise specified. (Continued)

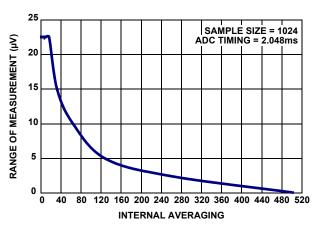

FIGURE 93. AUXILIARY SHUNT STABILITY: STDEV vs INTERNAL **AVERAGING**

The ISL28023 is a digital current, voltage and power monitoring device for high and low-side power monitoring in positive and negative voltage applications.

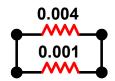

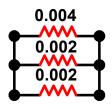

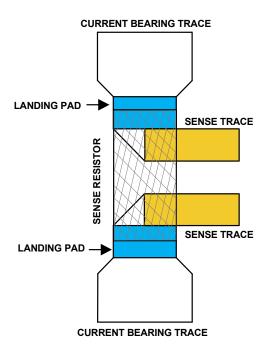

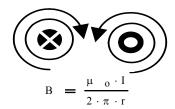

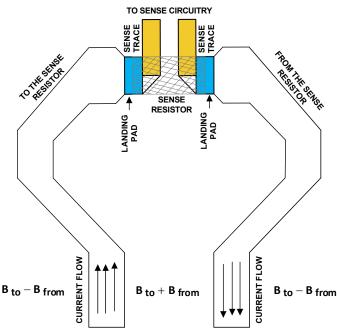

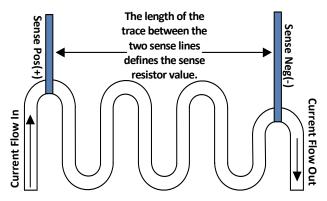

The Digital Power Monitor (DPM) requires an external shunt resistor to enable current measurements. The shunt resistor translates the bus current to a voltage. The DPM measures the voltage across the shunt resistors and reports the measured value out digitally via an I<sup>2</sup>C interface. A register within the DPM is reserved to store the value of the shunt resistor. The stored current sense resistor value allows the DPM to output a current value to an external digital device.

The ISL28023 has two channels, which allow the user to monitor the voltage, current and power on two power supply rails. The two channels for the DPM consist of a primary channel and an auxiliary channel. The primary channel will allow and measure voltages from OV to 60V or from OV to 16.384V, depending on the option of the ISL28023. The auxiliary channel can tolerate and measure voltage from OV to V<sub>CC</sub>.

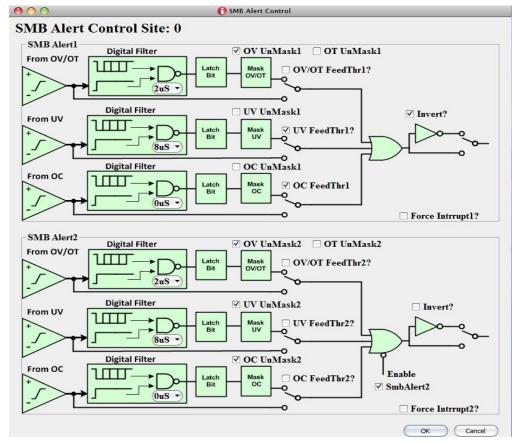

The ISL28023 has continuous fault detection for the primary channel. The DPM can be configured to set an alert in the instance of an overvoltage, undervoltage and/or overcurrent event. The response time of the alert is 500ns from the event. The ISL28023 has a temperature sensor with fault detection.

An 8-bit margin DAC, controllable through I<sup>2</sup>C communication, is incorporated into the DPM. The voltage margining feature allows for the adjustment of the regulated voltage to the load. The margin DAC can help in proving the load robustness versus the applied supply voltage.

The ISL28023 offers a 3.3V voltage regulator that can be used to power the chip in addition to low power peripheral circuitry. The DPM has an I<sup>2</sup>C power pin that allows the I<sup>2</sup>C master to set the digital communication supply voltage to the chip. The operating supply voltage for the DPM ranges from 3V to 5.5V. The device will accept I<sup>2</sup>C supply voltages between 1.2V and 5.5V.

FIGURE 94. AUXILIARY SHUNT STABILITY: RANGE vs INTERNAL **AVERAGING**

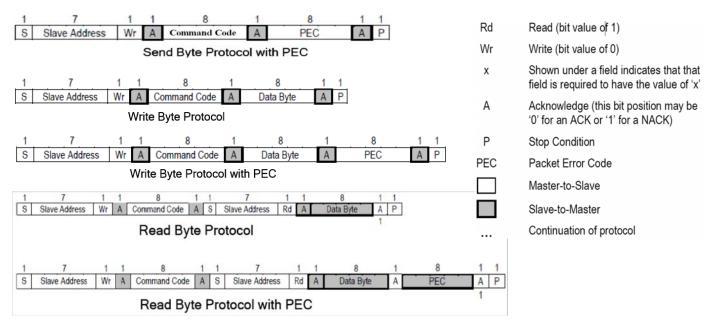

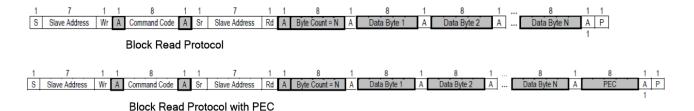

The ISL28023 accepts SMBus protocols up to 3.4MHz. The device is PMBus compliant up to 400MHz. The device has Packet Error Code (PEC) functionality. The PEC protocol uses an 8-bit cyclic redundance check (CRC-8) represented by the polynomial  $x^8+x^2+x^4+1$ . The ISL28023 can be configured for up to 55 unique slave addresses using 3 address select bits. The large amount of addressing allows 55 parts to communicate on a single I<sup>2</sup>C bus. It also gives the designer the flexibility to select a unique address when another slave address conflicts with the DPM on the same I<sup>2</sup>C bus.

# **Pin Descriptions**

#### **VBUS**

VBUS is the power bus voltage input pin. The pin should be connected to the desired power supply bus to be monitored. The voltage range for the pin is from OV to 60V or OV to 16V depending on the ISL28023 version.

#### **VINP**

VINP is the shunt voltage monitor positive input pin. The pin connects to the most positive voltage of the current shunt resistor. The voltage range for the pin is from OV to 60V or OV to 16V depending on the ISL28023 version. The maximum measurable voltage differential between VINP and VINM is 80mV.

## **VINM**

VINM is the shunt voltage monitor negative input pin. The pin connects to the most negative voltage of the current shunt resistor. The voltage range for the pin is from OV to 60V or OV to 16V depending on the ISL28023 version. The maximum measurable voltage differential between VINP and VINM is 80mV.

#### **AUXV**

AUXV is the power bus voltage input pin. The pin should be connected to the desired power supply bus to be monitored. The voltage range for the pin is from OV to V<sub>CC</sub>.

Submit Document Feedback intersil FN8389.5 27

#### **AUXP**

AUXP is the auxiliary shunt voltage monitor positive input pin. The pin connects to the most positive voltage of the auxiliary current shunt resistor. The voltage range for the pin is from OV to V<sub>CC</sub>. The maximum measurable voltage differential between AUXP and AUXM is 80mV.

#### **AUXM**

AUXM is the auxiliary shunt voltage monitor negative input pin. The pin connects to the most negative voltage of the auxiliary current shunt resistor. The voltage range for the pin is from OV to V<sub>CC</sub>. The maximum measurable voltage differential between AUXP and AUXM is 80mV.

#### VCC

VCC is the positive supply voltage pin. VCC is an analog power pin. VCC supplies power to the device. The allowable voltage range is from 3V to 5.5V.

#### **I2CVCC**

I2CVCC is the positive supply voltage pin. I2CVCC is an analog power pin. I2CVCC supplies power to the digital communication circuitry, I<sup>2</sup>C, of the device. The allowable voltage range is from 1.2V to 5.5V.

#### **GND**

Device ground. For single supply systems, the pin connects to system ground. For dual supply systems, the pin connects to the negative voltage supply in the system.

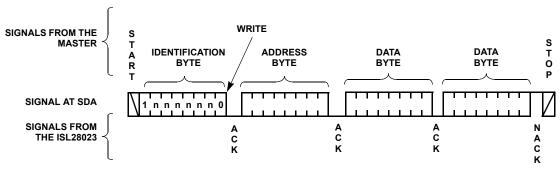

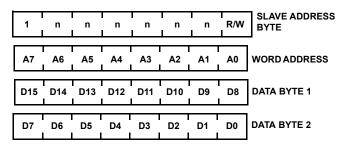

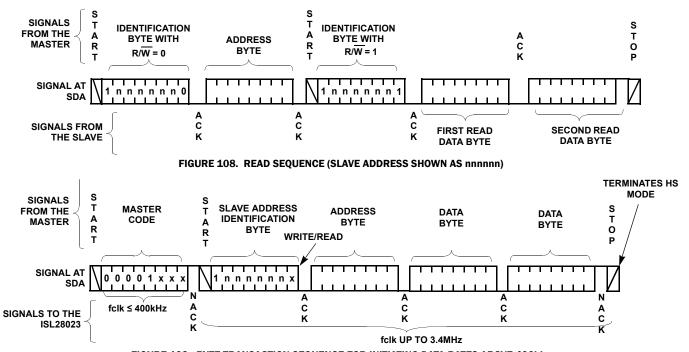

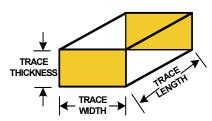

## **VREG IN**